# SELF-POWERED BALUN LOW NOISE AMPLIFIER WITH DEGENERATION BALANCING AND THERMAL NOISE ANALYSIS

by

Qusai Mohammad Abubaker

A Thesis presented to the Faculty of the American University of Sharjah

College of Engineering

In Partial Fulfillment

of the Requirements

for the Degree of

Master of Science in Electrical Engineering

Sharjah, United Arab Emirates

May 2020

# **Declaration of Authorship**

I declare that this thesis is my own work and, to the best of my knowledge and belief, it does not contain material published or written by a third party, except where permission has been obtained and/or appropriately cited through full and accurate referencing.

Signature ...Qusai Mohammad Abubaker.....

Date...May 10<sup>th</sup>, 2020....

The Author controls copyright for this report.

Material should not be reused without the consent of the author. Due acknowledgement should be made where appropriate.

© Year 2020 Qusai Mohammad Abubaker ALL RIGHTS RESERVED

# **Approval Signatures**

We, the undersigned, approve the Master's Thesis of Qusai Mohammad Abubaker.

Thesis Title: Self-Powered Balun Low Noise Amplifier with Degeneration Balancing and Thermal Noise Analysis.

Date of Defense: May 10<sup>th</sup>, 2020

#### Name, Title and Affiliation

**Signature**

Dr. Lutfi Albasha Professor, Department of Electrical Engineering Thesis Advisor

Dr. Oualid Hammi Professor, Department of Electrical Engineering Thesis Committee Member

Dr. Soliman Mahmoud Professor, Department of Electrical Engineering University of Sharjah Thesis Committee Member

Dr. Nasser Qaddoumi Head Department of Electrical Engineering

Dr. Lotfi Romdhane Associate Dean for Graduate Studies and Researcl College of Engineering

Dr. Sirin Tekinay Dean College of Engineering

Dr. Mohamed El-Tarhuni Vice Provost for Graduate Studies Office of Graduate Studies

#### Acknowledgement

I would like to thank my family for their support, prayer and sacrifice for my education. I would like to thank my aunt Huda for all her late-night motivational speeches, encouraging words, love and support. I would like to thank my friends Mohammed Al-Sabbagh and Khalid Baghdadi for their constant support and advice. Also, my friend Omar Kasimieh for helping me stay in a good physical condition and his life advices. Finally, special thanks to Ahmed Taha, Karam Jarad and Michel Bakouny for all the fun gaming time we had.

I would like to thank my advisor Prof. Lutfi Albasha for providing knowledge, guidance, support, and motivation throughout my research stages. I am deeply beholden for his great assistance, worthy discussion and suggestions. I would also thankful for the American University of Sharjah for supplying a scholarship and funding for my Master's degree.

I would like to thank the professors of the Electrical Engineering department who taught me the master level courses with mighty teaching methods and skills. I am really appreciating their dignified advices and motivation.

#### **Abstract**

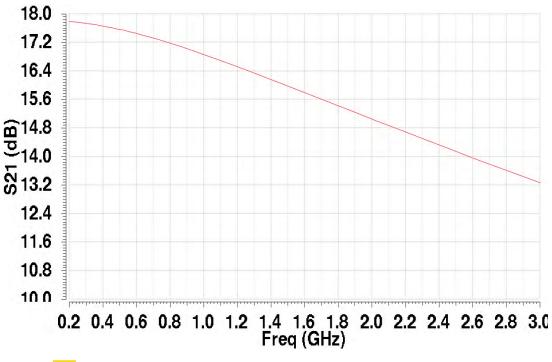

The Balun low noise amplifier (LNA) is an LNA that exploits a combination of a common-source (CS) and a common-gate (CG) transistor, which cancels the noise and distortion of the CG stage. And since the CG is known to be linear, only the CS needs to be carefully designed and optimized. In this thesis, the CS section will be fully analyzed, and shown how the condition set in the literature review still satisfies the balancing output and cancels the CS stage thermal noise as well as the CG thermal noise. Also, forward body biasing (FBB) is used to reduce the threshold voltage and in addition, CS degeneration resistor will be studied to balance the output and cancel the thermal noise of the transistors. The circuit is tested using UMC180nm on Cadence. The LNA achieves a gain of 19-16dB, NF<3.6 dB over the bandwidth 0.2-1.9GHz without a CS degeneration. A 17.8-14.8dB gain, a NF<3.8 dB over the bandwidth 0.2-2.1GHz and power consumption of 12mW in both cases. Although outside the bandwidth, at ISM 2.4GHz a gain of 14.5dB and a NF of 3.8 is achieved, making it suitable for wireless sensor node (WSN) applications. According to the authors' knowledge, this is the first time the degeneration resistor noise analysis on a Balun LNA is derived and simulated. Also, an RF harvester will be studied and used to power the Balun LNA. A two stage Dickson charge pump using MOSFET connected diode is chosen for this application. Although the efficiency is around 40%, the harvester was successfully integrated to the LNA, and its noise figure added to the output of the LNA.

Keywords: Low noise amplifiers; Balun; Noise analysis; Differential amplifiers; Degeneration; Harvester

# **Table of Contents**

| Abstract                      |                                                                    | 5                 |

|-------------------------------|--------------------------------------------------------------------|-------------------|

| List of F                     | igures                                                             | 8                 |

| List of T                     | ables                                                              | .11               |

| List of A                     | Abbreviations                                                      | .12               |

| Chapter                       | 1. Introduction                                                    | .14               |

| 1.1                           | Overview                                                           | .14               |

| 1.2                           | Organization                                                       | .15               |

| 1.3                           | Objective                                                          | .15               |

| 1.4                           | Contribution                                                       | .15               |

| Chapter                       | 2. Background                                                      | .16               |

| 2.1<br>Receiv<br>2.1.<br>2.1. | Receiver Architectures: Super-Heterodyne, Homodyne and Low-IF vers | .16<br>.16<br>.17 |

| 2.2                           | Harmonics and Intermodulation Distortions                          | .21               |

| 2.3                           | 1-dB Compression Point (P1dB)                                      | .22               |

| 2.4                           | 3 <sup>rd</sup> Order Intercept Point (IP3)                        | .22               |

| 2.5                           | Scattering Parameters (S-parameters)                               | .23               |

| 2.6                           | Process, Voltage and Temperature Variations (PVT)                  | .25               |

| 2.7                           | Forward Body Biasing (FBB).                                        | .27               |

| Chapter                       | 3. Low Noise Amplifiers                                            | .31               |

| 3.1.<br>3.1.                  | Noise                                                              | .31<br>.31<br>.36 |

| 3.2                           | Low Noise Amplifiers                                               | .37               |

| 3.3.<br>3.3.<br>3.3.          | LNA Topologies                                                     | .38<br>.40<br>.41 |

| 3.4                           | Balun LNA Noise Analysis                                           | .47               |

|             | 1.1 Noise analysis without degeneration resistor:                                 |      |

|-------------|-----------------------------------------------------------------------------------|------|

| 3.5         | Simulation of Balun LNA with Degeneration                                         | 55   |

| 3.6<br>Sour | Process-Voltage-Temperature Variation with Degeneration and Voltage ce as Biasing | 63   |

| 3.7         | Process Analysis without Degeneration and Current Mirror as Biasing               | 66   |

| Chapte      | r 4. RF Energy Harvester                                                          | 69   |

| 4.1         | Controlled Energy Source                                                          | 69   |

| 4.2         | Uncontrolled RF Energy Source                                                     |      |

| 4.3         | Charge Pump Rectifier                                                             | 70   |

| 4.4         | Dickson Charge Pump                                                               |      |

| 4.5         | Harvester Sizing and Stages Optimization                                          |      |

| 4.6         | Capacitors and FBB for the Harvester.                                             |      |

| 4.7         | Harvester number of stages                                                        |      |

|             | 7.1 One stage CPR testing:                                                        | 78   |

|             | 7.3 Three stage CPR testing:                                                      |      |

| Chapte      | r 5. LNA and Harvester Integration and Results                                    | 81   |

| 5.1         | Harvester Output Voltage, Current and Power                                       | 82   |

| 5.2         | LNA Simulation                                                                    | 88   |

| 5.3         | LNA and Harvester PVT                                                             | 93   |

| 5.4         | Stability and PVT of each side of the System                                      | 96   |

| 5.4         | 1.1 Common-gate at low frequencies (center @500MHz):                              |      |

| 5.4         | 1.2 Common-source at low frequencies (center @500MHz)                             | 98   |

| 5.4         | 4.3 Common-gate at high frequencies (center @2.1GHz):                             | 99   |

| 5.4         | 3.3 Common-source at high frequencies (center@2.1GHz):                            | .100 |

| Chapte      | r 6. Conclusion                                                                   | .102 |

| Referen     | nces                                                                              | .104 |

| Vita        |                                                                                   | 100  |

# **List of Figures**

| Figure 3.1 Resistor thermal noise model.                                        | 31 |

|---------------------------------------------------------------------------------|----|

| Figure 3.2 Common gate small signal model with thermal noise                    |    |

| Figure 3.3 Common gate small signal model with source resistor thermal noise    |    |

| Figure 3.4 Common gate small signal model with thermal noise and channel length |    |

| modulation                                                                      |    |

| Figure 3.5 Common gate small signal model with source resistance thermal noise  |    |

| channel length modulation                                                       |    |

| Figure 3.6 LNA trade-offs.                                                      | 38 |

| Figure 3.7 Common-Source with parasitic capacitors shown                        |    |

| Figure 3.8 Common-Gate with parasitic capacitors shown                          |    |

| Figure 3.9 Cascode structure.                                                   | 41 |

| Figure 3.10 CS differential pair.                                               | 42 |

| Figure 3.11 CG differential pair                                                |    |

| Figure 3.12 Balun LNA.                                                          | 43 |

| Figure 3.13 Balun LNA equations and graphs                                      |    |

| Figure 3.14 Improved Balun.                                                     | 45 |

| Figure 3.15 Balun LNA small signal model with thermal noise.                    | 47 |

| Figure 3.16 Balun LNA small signal model with thermal noise and CS degenerati   | on |

| resistor                                                                        |    |

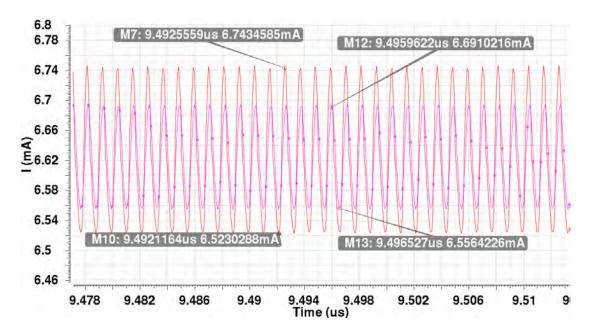

| Figure 3.17 Balun LNA using UMC180nm NMOS with degeneration resistor            | 56 |

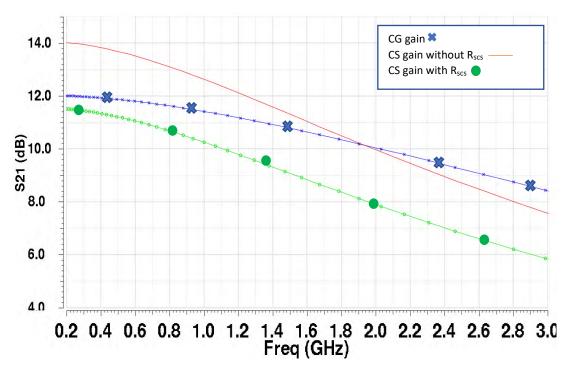

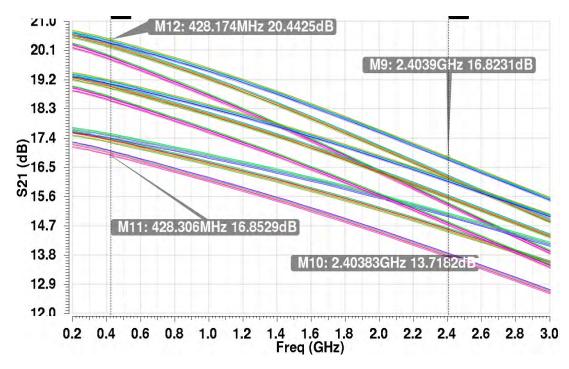

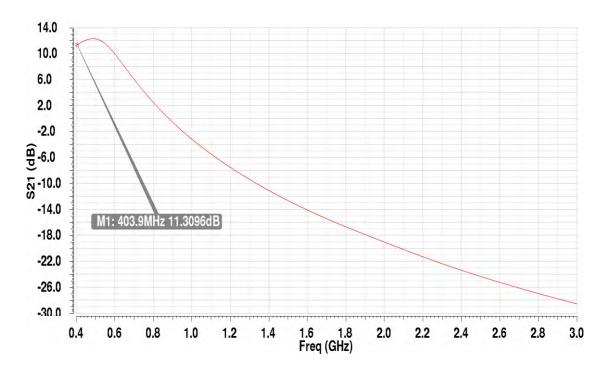

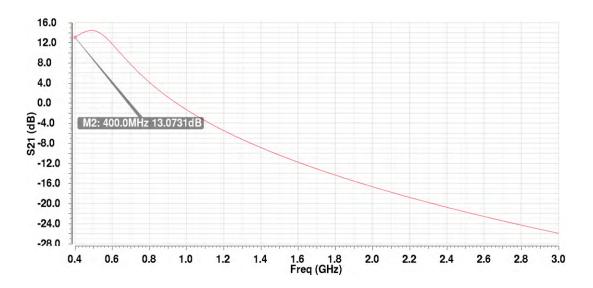

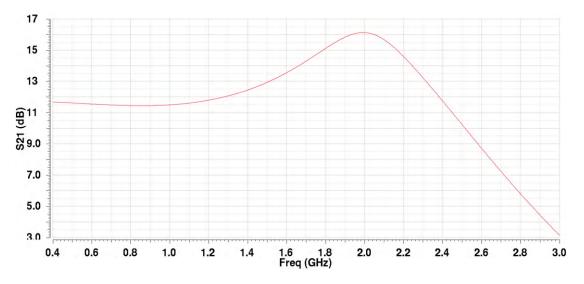

| Figure 3.18 S21 of CG, CS without degeneration and CSS with degeneration        | 57 |

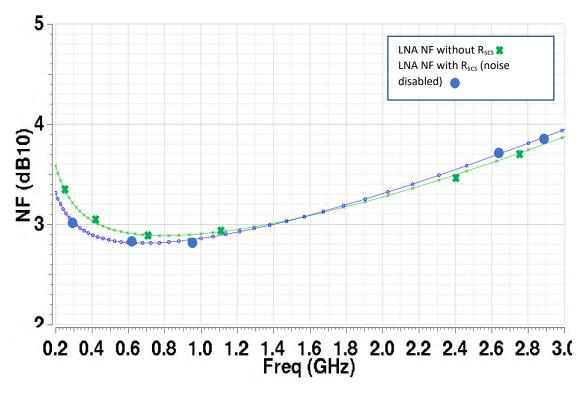

| Figure 3.19 LNA NF with CS degeneration noise disabled and without CS           |    |

| degeneration                                                                    | 58 |

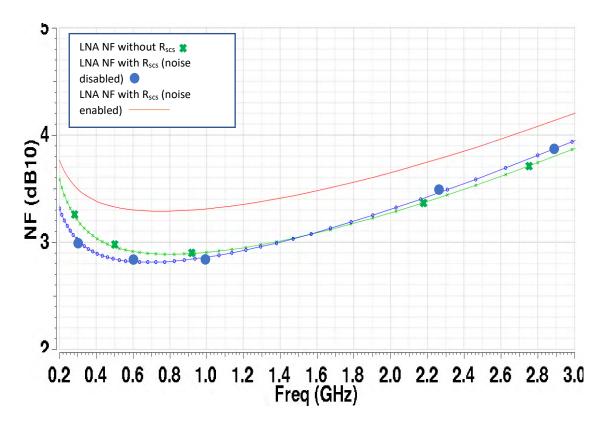

| Figure 3.20 NF of the LNA without degeneration and with degeneration (noise     |    |

| enabled and disabled)                                                           | 59 |

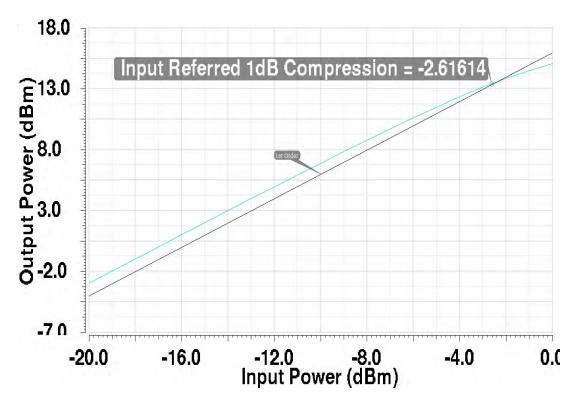

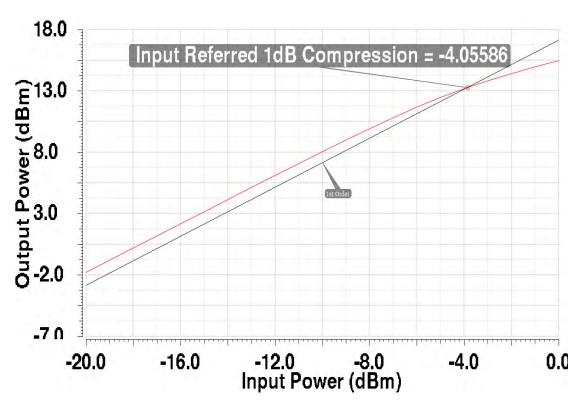

| Figure 3.21 P1dB with Rscs, -2.6dBm @900MHz                                     | 60 |

| Figure 3.22 P1dB without Rscs4.05dBm @900MHz                                    | 60 |

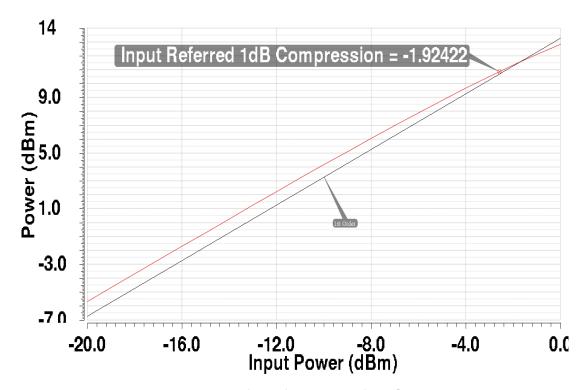

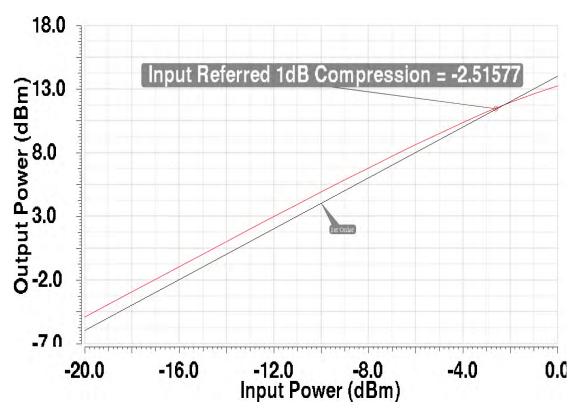

| Figure 3.23 P1dB with Rscs1.9dBm @2.4GHz                                        | 61 |

| Figure 3.24 P1dB without Rscs2.5dBm @2.4GHz                                     | 61 |

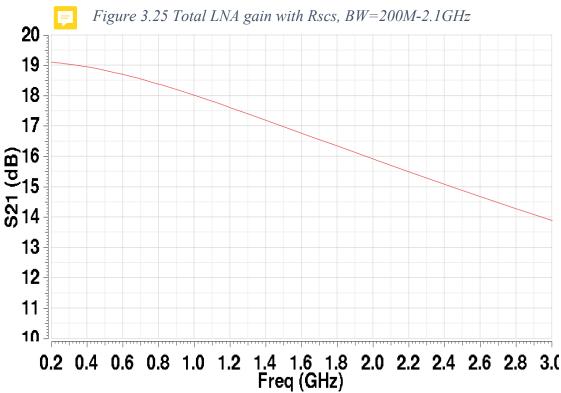

| Figure 3.25 Total LNA gain with Rscs, BW=200M-2.1GHz                            | 62 |

| Figure 3.26 Total LNA gain without Rscs, BW=200M-1.9GHz                         |    |

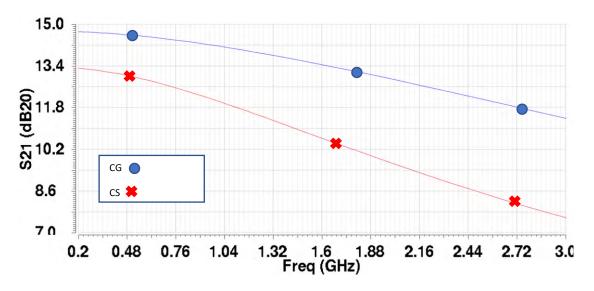

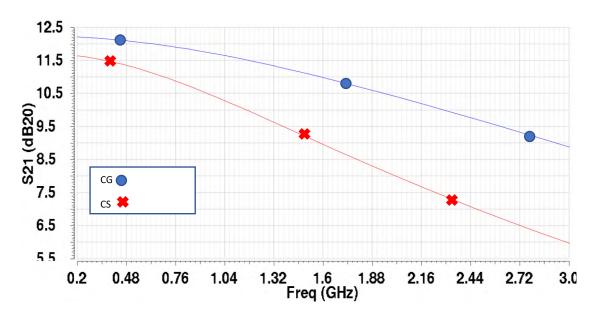

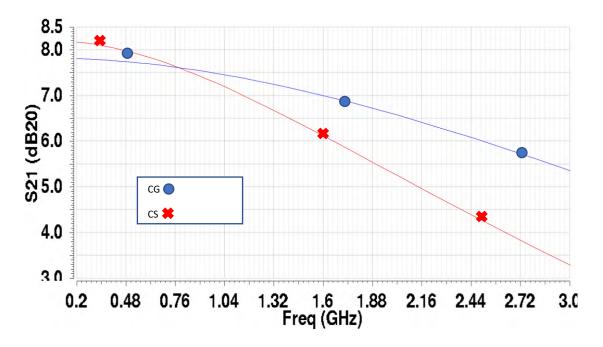

| Figure 3.27 CS and CG gain at fast corners at -40°C                             | 64 |

| Figure 3.28 CS and CG gain at typical corners at 27°C                           | 64 |

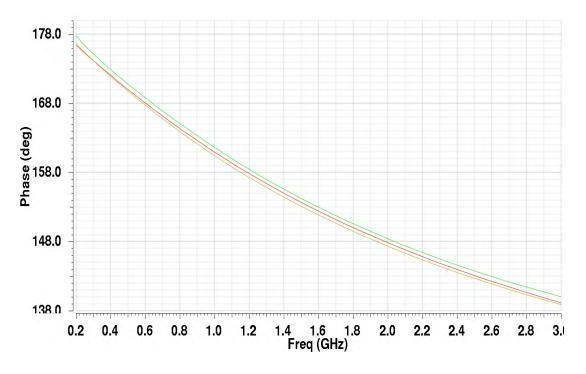

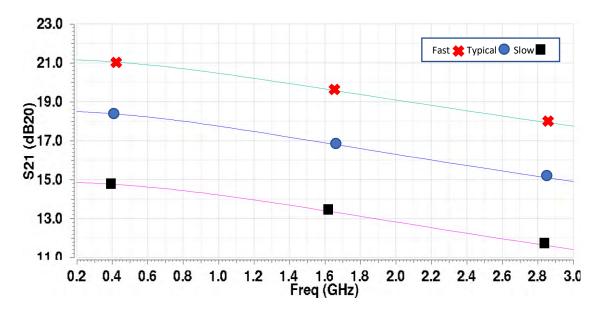

| Figure 3.31 Total LNA gain at fast (-40°C), typical (27°C) and slow (85°C)      | 66 |

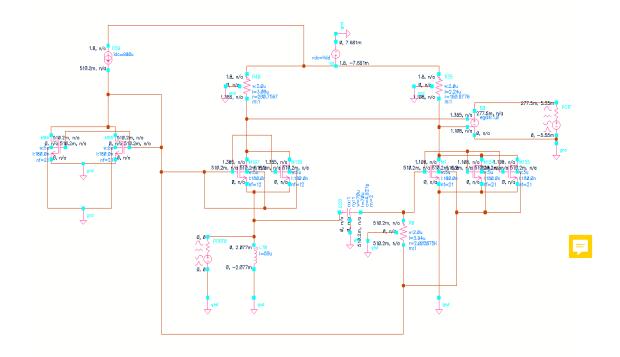

| Figure 3.32 LNA schematic from Cadence (with inverted colors)                   | 67 |

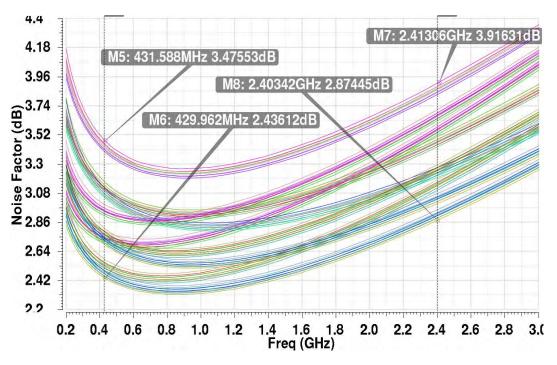

| Figure 3.33 Noise of every single possible corner analysis at 27°C              | 67 |

| Figure 3.34 Gain of every single possible corner analysis at 27°C               | 68 |

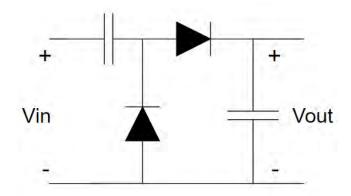

| Figure 4.1 Rectifier circuit using diodes                                       | 71 |

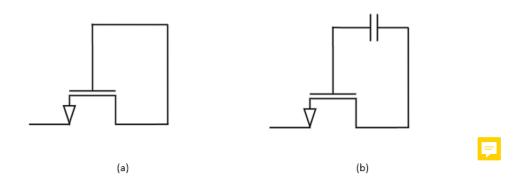

| Figure 4.2 (a) Diode connected MOSFET (b) Floating gate configuration           | 72 |

| Figure 4.3 Dickson charge pump circuit                                          |    |

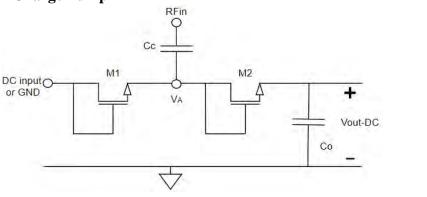

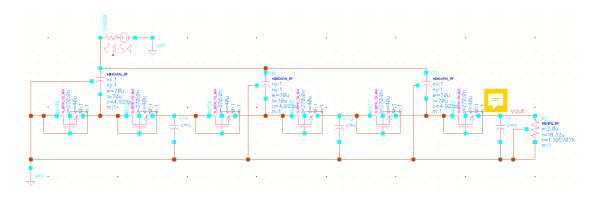

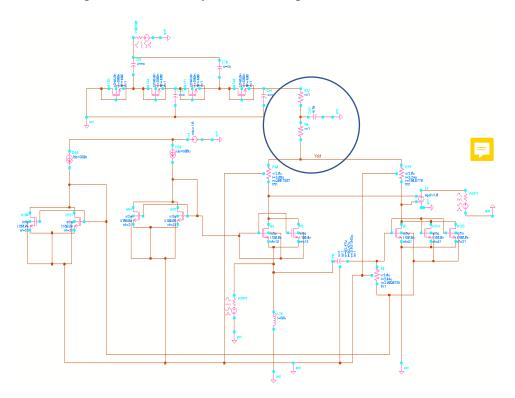

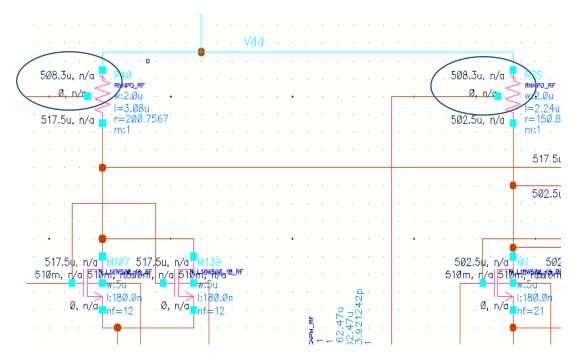

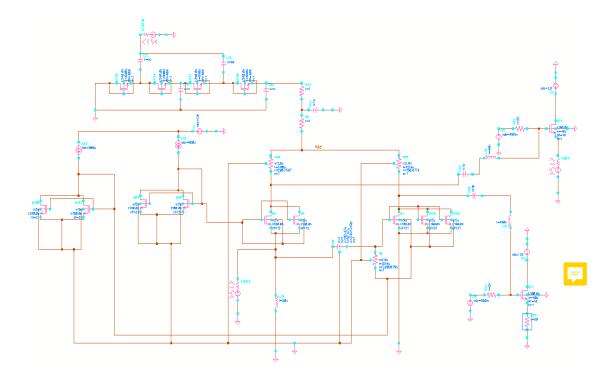

| Figure 4.4 Cadence schematic image of three stage Dickson charge pump           | 74 |

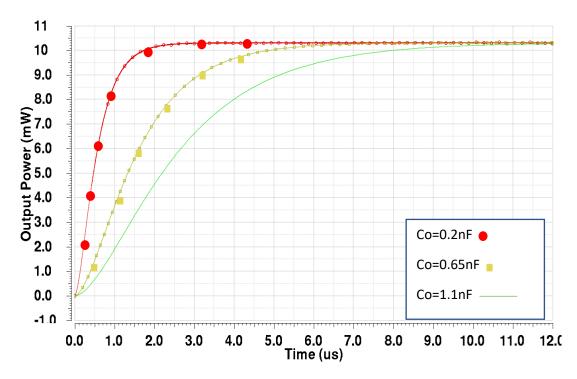

| Figure 4.5 Different load capacitor value vs charge time                        |    |

|                                                                                 |    |

| 8                                                                               |    |

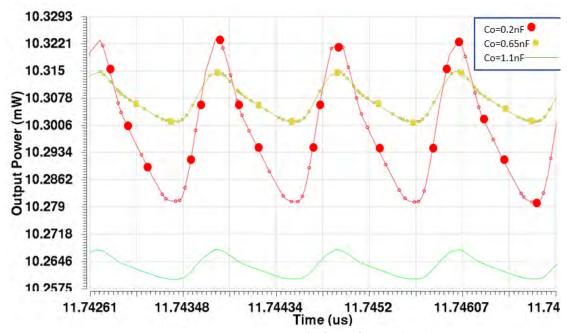

| Figure 4.6 Capacitors ripple from figure (7.37)                                       | 76   |

|---------------------------------------------------------------------------------------|------|

| Figure 4.7 Low threshold transistor with FBB and without FBB. An efficiency           |      |

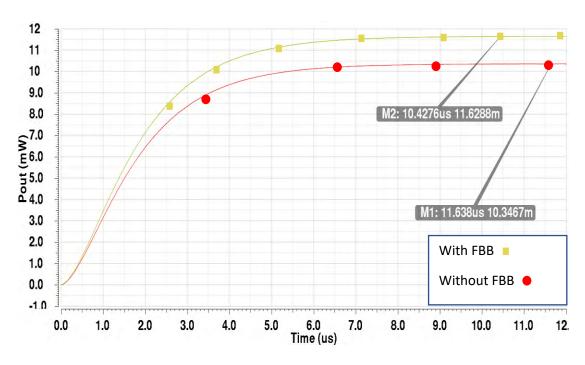

| increase is noticed with FBB.                                                         | 77   |

| Figure 4.8 1-stage Dickson charge pump                                                | 78   |

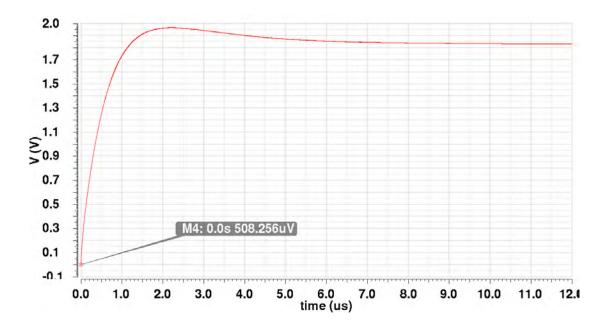

| Figure 4.9 One stage harvester output with input of 15mW @900MHz                      | 79   |

| Figure 4.10 2-stage Dickson charge pump                                               | 79   |

| Figure 4.11 Two stage harvester output with input of 50mW @900MHz                     | 80   |

| Figure 4.12 3-stage Dickson charge pump                                               | 80   |

| Figure 4.13 Three stage harvester output with input of 126mW @900MHz                  | 81   |

| Figure 5.1 Full schematics of LNA and the harvester from Cadence view                 | 82   |

| Figure 5.2 The two resistors are 1-Ohms each and only used to measure current. The    | he   |

| capacitor is the smoothing capacitor                                                  | 83   |

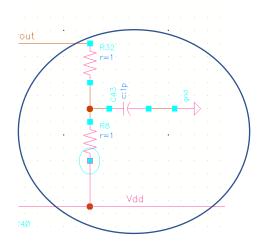

| Figure 5.3 Simplified schematics of LNA and harvester using Visio                     | 83   |

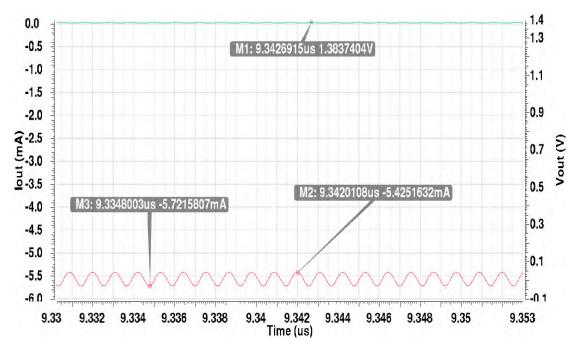

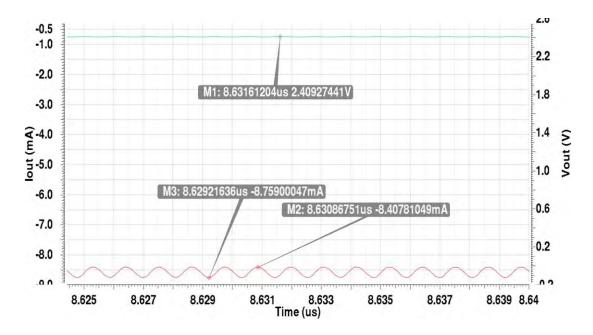

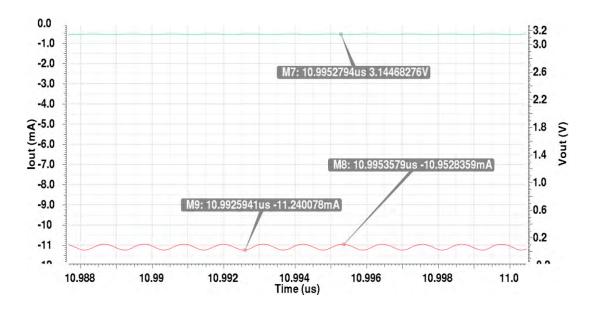

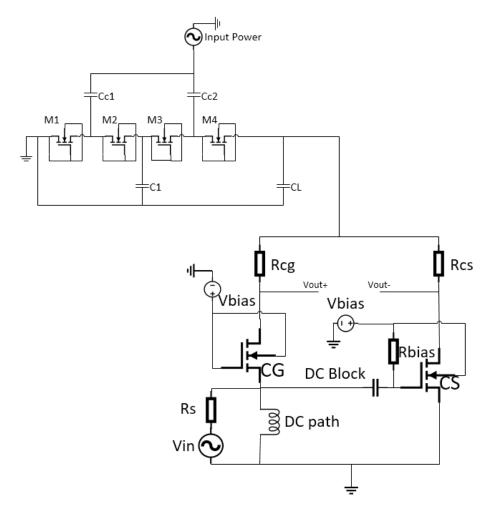

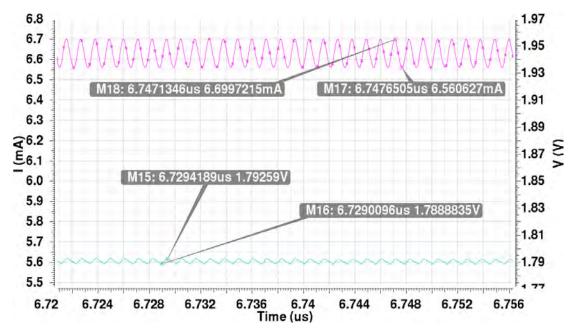

| Figure 5.4 Output current before and after the addition of the smoothing capacitor,   | , a  |

| reduction in output swing is noticed.                                                 | 84   |

| Figure 5.5 Final output of the harvester, the swing is due to non-ideality of the     |      |

| rectification stage.                                                                  | 84   |

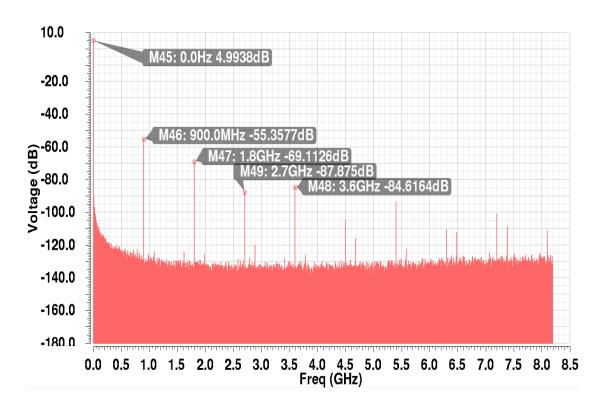

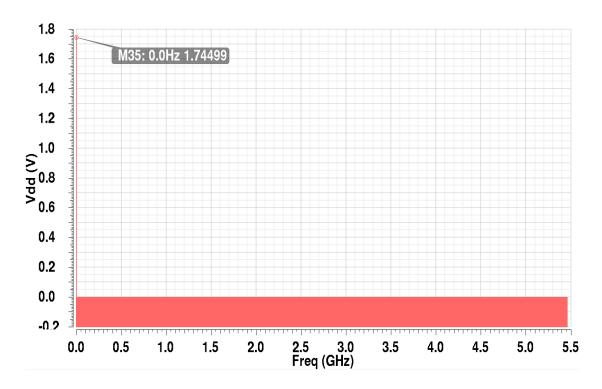

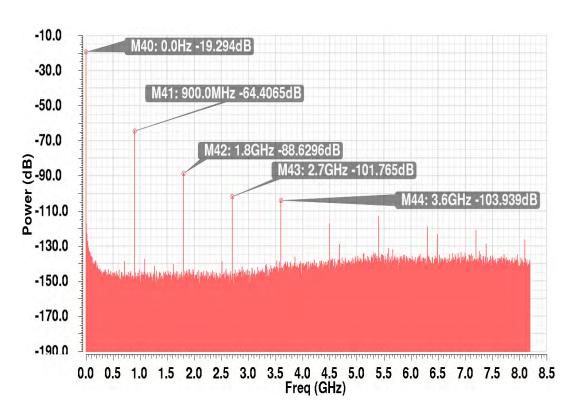

| Figure 5.6 Output voltage harmonics in dB.                                            | 85   |

| Figure 5.7 Output voltage harmonics in volts                                          | 86   |

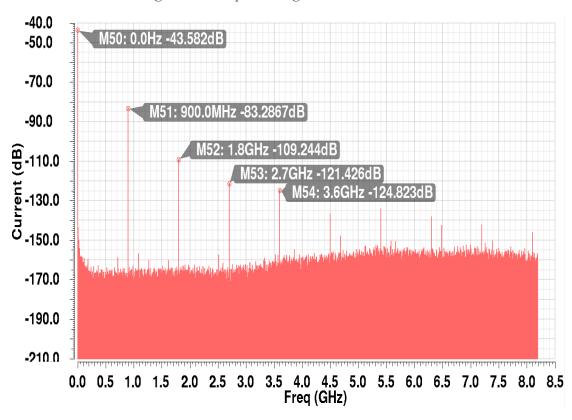

| Figure 5.8 Output current harmonics in dB.                                            | 86   |

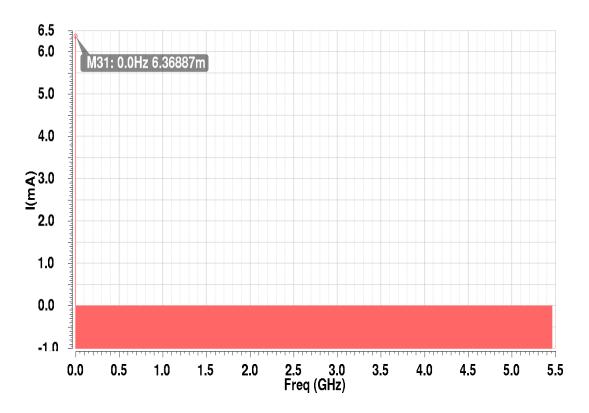

| Figure 5.9 Output current harmonics in mA                                             | 87   |

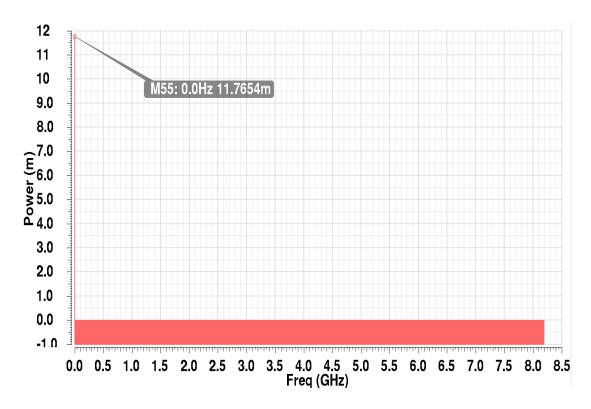

| Figure 5.10 Output power harmonics in dB                                              |      |

| Figure 5.11 Output power harmonics in mW.                                             | 88   |

| Figure 5.12 The "DC annotate" values in the Cadence schematic window                  | 89   |

| Figure 5.13 The value of the "DC" simulation is the zero second value                 | 89   |

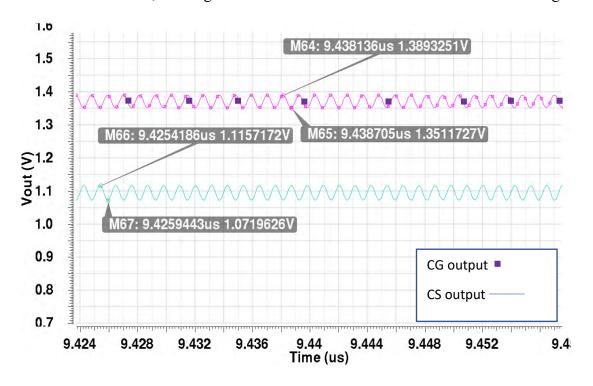

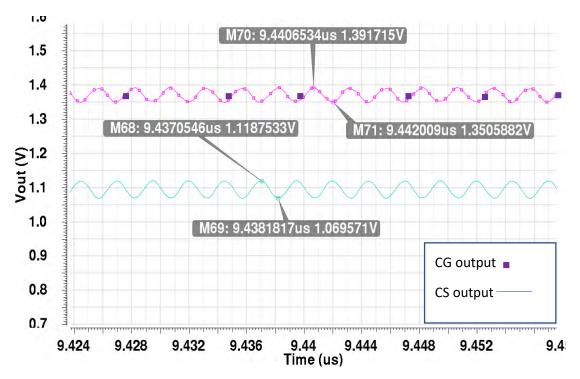

| Figure 5.14 CG and CS output with an input of 10mV @900MHz. "Transient"               |      |

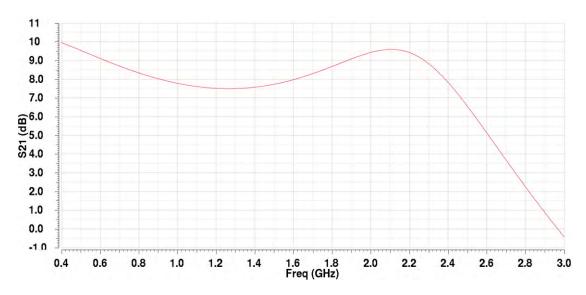

| simulation is used. CG gain=11.63dBV, CS gain = 12.8dBV                               | 90   |

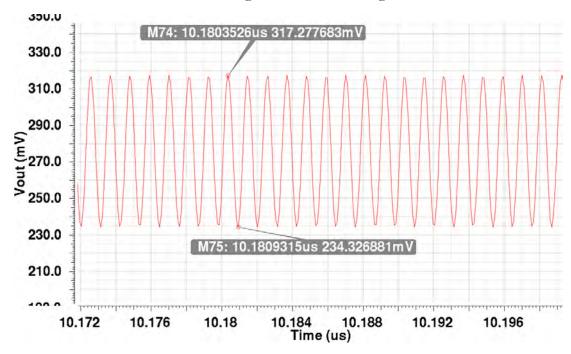

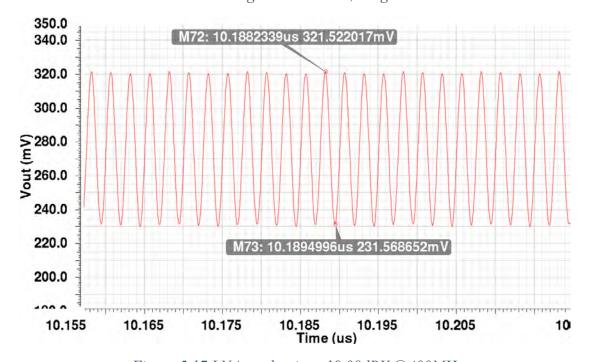

| Figure 5.15 LNA total gain = 18.38dBV @900MHz                                         | 90   |

| Figure 5.16 CG and CS output with an input of 10mV @400MHz. "Transient"               |      |

| simulation is used. CG gain=12.28dBV, CS gain = 13.84dBV                              | 91   |

| Figure 5.17 LNA total gain = 19.08dBV @400MHz                                         | 91   |

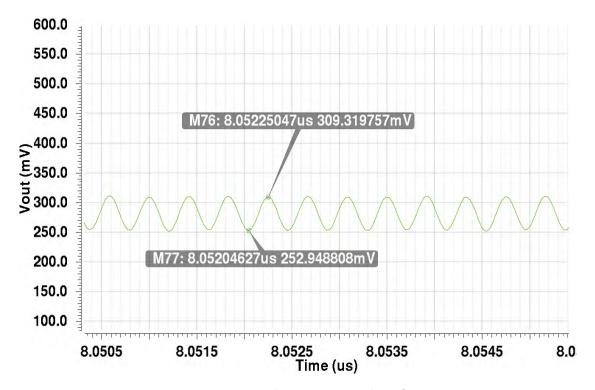

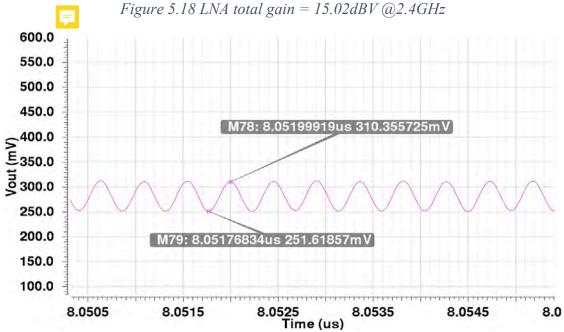

| Figure 5.18 LNA total gain = 15.02dBV @2.4GHz                                         | 92   |

| Figure 5.19 LNA total gain = 15.37dBV @2.2GHz                                         | 92   |

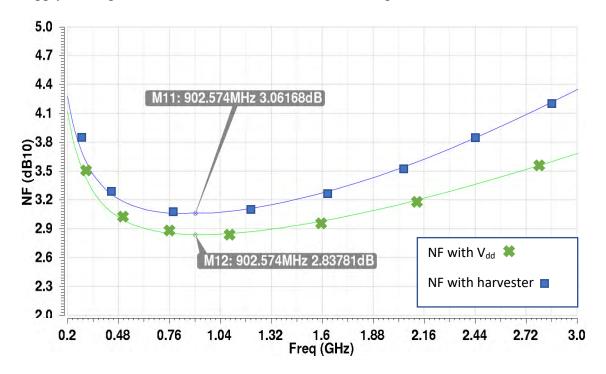

| Figure 5.20 NF of the LNA with and without the Harvester, the harvester added a       |      |

| 0.2dB noise to the system. The noise of the harvester is related to PSRR              | 93   |

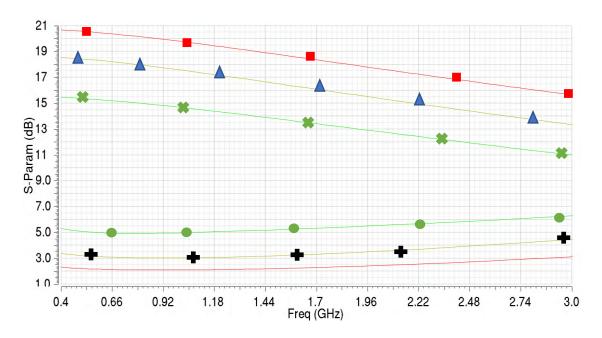

| Figure 5.21 The Gain and NF of the LNA when powered by the harvester                  | 94   |

| Figure 5.22 Legend for figure (5.21)                                                  | 94   |

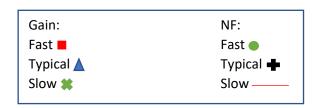

| Figure 5.23 S11 at all three corners.                                                 | 94   |

| Figure 5.24 Corner analysis for the circuit. Green, yellow and red colors are pass, 1 | near |

| and failing specification, respectively                                               | 95   |

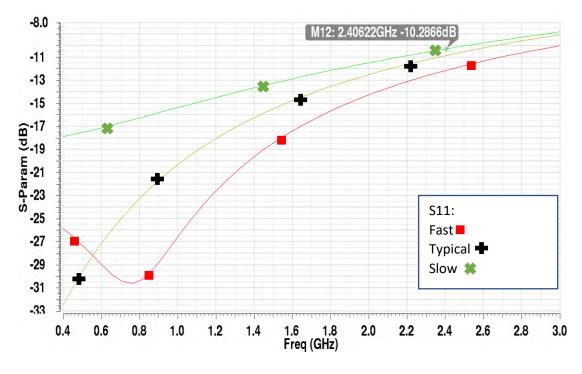

| Figure 5.25 P1dB at the three corners.                                                | 95   |

| Figure 5.26 LNA and Harvester with buffers circuit.                                   | 96   |

| Figure 5.27 CG gain at typical corners with buffers                                   | 97   |

| Figure 5.28 Corner analysis and stability of CG at low frequencies                    | 98   |

| Figure 5.29 CS gain at typical corners with buffers.                                  | 98   |

| Figure 5.30 Corner analysis and stability of the CS at low frequencies  | 99  |

|-------------------------------------------------------------------------|-----|

| Figure 5.31 CG gain at typical corners with buffers                     | 99  |

| Figure 5.32 Corner analysis and stability of the CG at high frequencies | 100 |

| Figure 5.33 CS gain at typical corners with buffers.                    | 100 |

| Figure 5.34 Corner analysis and stability of the CS at high frequencies | 101 |

# **List of Tables**

| Table 1. Advantages and Disadvantages of the super-heterodyne receiver              | 17 |

|-------------------------------------------------------------------------------------|----|

| Table 2. Advantages and Disadvantages of the Homodyne receiver                      | 18 |

| Table 3. Advantages and Disadvantages of the Low-IF receiver                        | 20 |

| Table 4. FBB Vth value                                                              | 28 |

| Table 5. Balun LNA circuit details                                                  | 56 |

| Table 6. Comparison with the state of the art LNA                                   | 63 |

| Table 7. Zero threshold, Triple well and Low threshold transistors comparison       | 77 |

| Table 8. Different stages of harvester for low threshold transistor comparison with | 1  |

| LNA as the load.                                                                    | 81 |

#### **List of Abbreviations**

AC Alternating current

CG Common Gate

CMOS Complementary-Channel Metal-Oxide-Semiconductor

CPR Charge Pump Rectifier

CS Common Source

dB Decibels

DC Direct current

DRC Direct conversion

DSP Digital Signal Processing

FBB Forward Body Biasing

G Gain

IF Intermediate frequency

IIP3 Input referred IP3

IMD Intermodulation distortion

IP3 Third order intercept point

LNA Low-Noise Amplifier

LO Local oscillator

LPF Low pass filter

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NF Noise figure

NMOS N-channel Metal-Oxide-Semiconductor

OIP3 Output referred IP3

P1dB 1-dB compression point

PDK Process Design Kit

PMOS P-channel Metal-Oxide-Semiconductor

RF Radio frequency

ULP Ultra-Low Power

ULV Ultra-Low Voltage

UMC United Microelectronics Cooperation

WSN Wireless sensor nodes

ZIF Zero Intermediate frequency

#### **Chapter 1. Introduction**

# 1.1 Overview

The digital revolution in the wireless market has brought many changes in analog transceivers today. The wireless transceiver detects weak and high frequency signal, this requires high performance from RF and baseband analog circuits. The high performance required of the RF circuit working at high frequencies brings challenges to the circuit design. With the consideration of the price and power consumption, many researchers use Complementary MetalOxide Semiconductor (CMOS) technologies for Radio Frequency (RF) applications. CMOS Integrated Circuits (ICs) are low cost, low power consumption and better integration with DSP (Digital Signal Processing) chips. CMOS also allow a large amount of digital functions on a single die.

Energy Harvesting is defined as the practice of capture, accumulation and storage of unexploited energy from circumambient environmental sources. The field of energy harvesting is in rapid development and is the new hit in RF designs, as some devices are in positioned that are not easy to reach for battery replacements. RF wireless electronics perform a crucial role in gathering and analyzing information nowadays. To sustain the wireless data, many wireless infrastructures have been made and used, such as TV networks, GSM networks, etc. which can in theory be captured and stored. However, some circuits are being developed with certain efficiency which help them capture power from a source to charge them. This is a more realistic approach to energy harvesting, as a harvester can be optimized at certain power levels and frequency [1].

To have a Wireless sensor network (WSN), several different sensor nodes are energetically autonomous and wirelessly connected. They share information by communicating wirelessly. The transceiver connects the individual nodes together, thus a wireless sensoring network is made. WSN area and installation depend on their characteristics and range. Additionally, these nodes must be autonomous and individually power, the problem when installing batteries to make any sensor node autonomous is that these nodes are in harsh environments making battery replacement difficult, therefore energy harvesting devices are attractive to WSN applications to charge the battery or power the node directly. The idea of having a self-powered node also opens many possibilities for their geographical location.

After the transmitter modulates the signal, it is then transmitted. The process of modulation has the signal go from baseband frequencies to any higher desired frequency, usually the carrier frequency, this reduces the size of the antenna (antenna's length is typically wavelength/4). Also, as the signal propagates, it suffers from attenuations, thus, must be amplified by the receiver [2]. The frontend amplifier of the receiver known as the low noise amplifier (LNA) possess low noise properties, as the noise will propagate and get amplified going forward into the receiver, the LNA also has moderate gain to compensate for the propagation attenuation.

### Organization

The thesis is broken down to several chapters as follows: Chapter 2 is background discussing types of receivers, compression point, Intercept points, scattering parameters and process, voltage and temperature (PVT) analysis. Chapter 3 is noise analysis, LNA topologies and noise derivation of the current design. Chapter 4 is harvester topologies, design method and harvester testing and simulation for the current design. Chapter 5 is the LNA and harvester integration with all simulation results. Chapter 6 is the conclusion and future.

#### 1.3 Objective

The main objective of this thesis is to show how the Balun LNA thermal noise of the transistors can be completely canceled and not just the CG side. A degeneration resistor on the CS side of the Balun LNA is studied and shown how the degeneration balancing can cancel the thermal noise of the transistors completely.

A harvester is to be picked for the LNA to power it, while still maintaining the highest AC to DC conversion efficiency. Three transistors will be tested in terms of width, length, number of fingers and load to pick the most efficient one. The LNA will be directly connected to the harvester as a load, making the harvester directly power the circuit without any charge storing unit.

#### 1.4 Contribution

Not only does the thesis show how the thermal noise of the CS side of the Balun LNA is canceled, it also adds to it by showing how a degeneration resistor can help cancel the transistor thermal noise of the LNA, adding one more degree of freedom to the design. Also, a Dickson charge pump is used to directly power the LNA without any storage unit with its noise successfully added to the system.

#### Chapter 2. Background

In this chapter three receiver architectures are discussed with the advantages and disadvantage of each. Additionally, some measuring parameters, such as P1dB, IMD3, S-parameters etc. are explained.

# 2.1 Receiver Architectures: Super-Heterodyne, Homodyne and Low-IF Receivers.

A receiver main purpose is to detect an RF signal at the antenna, down convert it into an intermediate frequency (IF), maintain the signal quality and deliver it to the baseband. Super-heterodyne, homodyne and low-IF receivers advantages, and disadvantages are shown.

2.1.1 Super-heterodyne receiver: The RF signal is captured by the antenna and filtered through a bandpass filter which removes unwanted frequencies. The signal is too weak at this stage, therefore an LNA is used to amplify the signal and add as little noise as possible. The second filter is there for image rejection, all it does is attenuate the signal at image band frequencies. The first mixer is to down convert the signal to the IF band, the reason the signal is converted to IF or baseband is to lower the bandwidth and therefore becomes much easier and faster to process. A high selectivity filter that removes any adjacent IF signals from the desired IF which helps avoid image frequency issues. Finally, the signal is sent to the analog to digital converter (ADC) [3].

The image frequency problem occurs when the input of the mixer has a signal image, which after multiplication generates two other signals with one laying inside the IF, resulting in overlapping between the desired signal and an unwanted signal, the image and the signal are impossible to separate at this point. Therefore, before entering the mixer, an image rejection filter is applied to remove the image signal [2] [4], this is the only way to avoid image frequency issue.

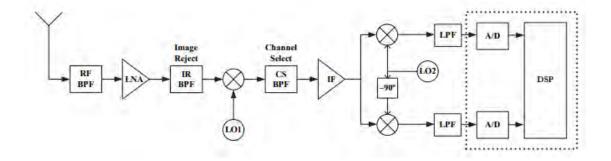

Figure (2.1) [5], is a schematic of the superhetrodyne receiver, showing all the components. Table 1 [3] lists the most important advantages and disadvantages of the superhetrodyne receiver.

Figure 2.1: Super-heterodyne Receiver.

*Table 1. Advantages and Disadvantages of the super-heterodyne receiver.*

| Advantage                             | Disadvantages                          |

|---------------------------------------|----------------------------------------|

| Well established                      | Image frequency                        |

| Superior performance                  | Difficult to integrate                 |

| Adjustable with discrete              | Costly (money and power)               |

| Good spurious suppression with filter | Requires quadrature generating complex |

|                                       | mixer                                  |

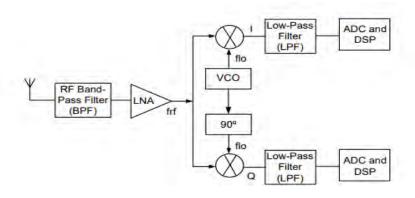

**2.1.2 Homodyne receiver.** The homodyne receiver is also known as the direct conversion receiver or the zero-IF receiver (ZIF), converting the RF to baseband directly, with less components than the super-heterodyne. This is done with an LO with the same frequency of the RF. The main advantages over the super-heterodyne is that the homodyne receiver does not generate image frequency, therefore no extra techniques to deal with the image are needed. Also, it is simpler in design and implantation, hence the reason why integrating it on chip is easier than the super-heterodyne receiver.

Figure (2.2) [5], is a schematic of the homodyne receiver, showing all the components. Table 2 [3] lists the most important advantages and disadvantages of the homodyne receiver.

Figure 2.2: Homodyne Receiver.

Table 2. Advantages and Disadvantages of the Homodyne receiver.

| Advantages                                                       | Disadvantages                                                                                                                          |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| No image, therefore, no need for a SAW filter                    | DC offset and flicker noise                                                                                                            |

| Highly integrable                                                | Significant LO leakage could create inband interference                                                                                |

| Only one PLL is needed                                           | Strong AM interference will create inband interference after the mixer, therefore a linear mixer is required                           |

| Low power                                                        | LO leakage to the antenna can be transmitted and reflected to self-mix with the oscillator creating a time varying wandering DC offset |

| Good multi-standard ability                                      | Leakages from the transmitter may need a good filter                                                                                   |

| Increased ADC dynamic range.  No IF, therefore limited filtering | I/Q match required to avoid imbalances which causes constellation distortion                                                           |

| Industry standard for mobile headsets                            | VCO requires multiple frequency of RF                                                                                                  |

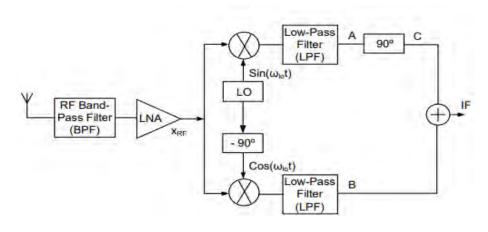

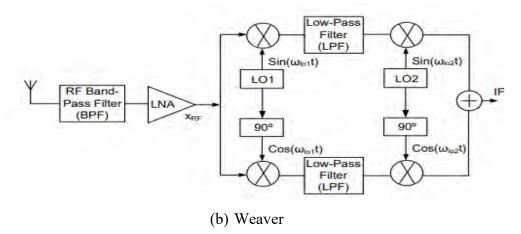

2.1.3 Low-IF receiver: If one tries to combine the advantages of the previous two architectures, the Low-IF receiver is formed. The DC problem of the homodyne receiver can be avoided by relaxing the quality factor of the channel selective filter, particularly flicker noise is dealt with. The image problem from the super-heterodyne can be canceled using special mixing circuits or the polyphase quadrature filters. Image cancelation techniques are implemented to avoid using image rejection filters. Two architectures are used, Weaver and Hartley, these methods suppress the image by its negative replica. The idea is to process the RF signal after LPF and combine both outputs into one. Figure (2.3) [6] is two different Low-IF receiver architectures and Table 3 [3] list the main advantage and disadvantages of this architecture.

$$x_{RF}(t) = V_{RF}\cos(w_{RF}t) + V_{IM}\cos(w_{IM}t)$$

(2.1)

$$y_A(t) = \frac{V_{RF}}{2} \sin[(w_{LO} - w_{RF})t] + \frac{V_{IM}}{2} \sin[(w_{LO} - w_{IM})t]$$

(2.2)

$$y_B(t) = \frac{V_{RF}}{2} \sin[(w_{LO} - w_{RF})t] + \frac{V_{IM}}{2} \sin[(w_{LO} - w_{IM})t]$$

(2.3)

$$\sin\left(\theta - \frac{\pi}{2}\right) = -\cos(\theta)$$

, with a 90° shift

$$y_c(t) = \frac{V_{RF}}{2} \sin[(w_{RF} - w_{LO})t] - \frac{V_{IM}}{2} \sin[(w_{LO} - w_{IM})t]$$

(2.4)

One where  $x_{RF}$  is the RF signal,  $V_{RF}$  is the voltage level of the RF signal,  $w_{RF}$  is the carrier angular frequency, t is time,  $V_{IM}$  is the voltage level of the Intermediate frequency,  $w_{IM}$  is the Intermediate angular frequency,  $w_{LO}$  is the local oscillator angular frequency, and y is the output.

# (a) Hartley

Figure 2.3: Low-IF Hartley and Weaver architectures.

When adding (2.3) and (2.4) the wanted signal is recovered and image is removed.

Weaver architecture has similar result but with a second mixer stage at IF. Both architectures can remove the image, depending on their quadrature signal precision. A draw back for these two designs is that having a quadrature error will result in gain/phase imbalances, making it difficult for the next stages to process the signal smoothly.

*Table 3. Advantages and Disadvantages of the Low-IF receiver.*

| Advantages                            | Disadvantages                            |

|---------------------------------------|------------------------------------------|

| Eliminates the need for external SAW  | Additional digital signal processing to  |

| same as homodyne                      | cope with Non-ZIF, requires ADC twice    |

|                                       | the BW compared to ZIF or                |

|                                       | superhetrodyne                           |

| No DC offset problem                  | Uses an additional phased locked loop to |

|                                       | get to I&Q                               |

| Suitable for CMOS as phased locked    | Only marginal rejection with polyphase   |

| loop operates around 2GHz             | filters                                  |

| Less RF filtering than homodyne       | Complex filter implementation            |

| receiver, but in-band image rejection | compared to homodyne receiver            |

# 2.2 Harmonics and Intermodulation Distortions

In a non-linear system its polynomials can be estimated as [3]:

$$y = a_0 + a_1 x + a_2 x^2 + a_3 x^3 + \cdots, (2.5)$$

where x is the input signal and y represent the output signal. Systems are usually not extremely nonlinear therefore higher order disappear.

If  $x = \sin(2\pi ft)$  is applied to a non-linear system input. The output result is approximately:

$$y = a_0 + a_1 A \sin(2\pi f t) + a_2 \frac{a_2 A^2}{2} \sin(4\pi f t) + \left(\frac{a_3 A^3}{4}\right) \sin(6\pi f t)$$

(2.6)

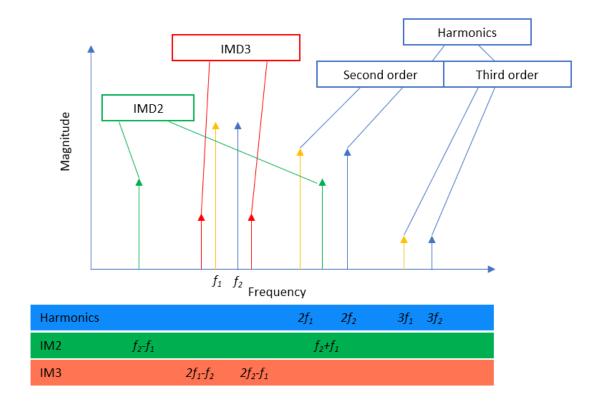

The expression in (2.6) has harmonic distortions at multiple fundamental frequencies. Harmonics can lead to reduction in filtering or can interfere with other channels. The second problem is intermodulation distortion (IMD). IMD is the amplitude modulation of multiple different frequencies caused by non-linearity of a system. If the  $2^{\rm nd}$  unwanted signal is not filtered out, the receiver will produce  $2^{\rm nd}$  order IMD and  $3^{\rm rd}$  order IMD which are  $f_2 \pm f_1$  and  $2f_2 \pm f_3$  respectively. Adding the coefficient of each  $f_n$  will give the order of the IMD. The most dangerous modulation is the  $3^{\rm rd}$  order, as it is near the operating frequency.

Harmonics and IMD are unavoidable phenomenon's and cannot be completely removed from a system. Harmonics might be harmful to a wideband system, but most importantly to other channels that the harmonics will be projected onto, therefore they cannot be ignored. IMD's, specifically IMD3, fall very close to the desired frequency of operation and can cause unwanted interfere if not properly dealt with, a very sharp filter can help reduce the IMD3 for an extra cost to the system. Figure (2.4) shows what harmonics and IMD are in graph format for a two-tone input  $(f_1 \text{ and } f_2)$ . Harmonics are integer multiple of the main frequency (or frequencies) they are infinite, but since the harmonic's magnitude is very low after the third harmonic they can be ignored. Although the second order harmonics have the highest magnitude, they are far away from the operation frequency and can be ignored. The same idea for ignoring the higher order of harmonics apply for IMD, where the IMD of higher order than three are either far away or too small and can be ignored.

Figure 2.4 Two-tone harmonics and IMD.

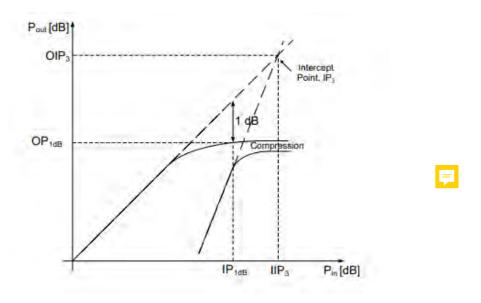

# 2.3 —1-dB Compression Point (P1dB)

will appear. P1dB is considered as a loss of power. In linear operation of an amplifier, increasing the input by 1 dB or 10 dB should not result in any change in the gain, however at the P1dB the amplifier no longer acts linearly, rather starts to get saturated and the amplifier experiences a loss of 1 dB in gain. Similarly, PXdB is when the amplifier loses X-dB of the output gain. At this point the amplifier has left the linear operation region.

#### 2.4 3rd Order Intercept Point (IP3)

Another important figure to test is the third order intermodulation intercept point (IP<sub>3</sub>), which is a measure of the linearity of the system. IIP<sub>3</sub> is the input referred IP<sub>3</sub> and OIP<sub>3</sub> is the output referred IP<sub>3</sub>. The IP<sub>3</sub> is the intersection of the idealized output power of the first and third order, at this point the first and third order are of equal power. IP<sub>3</sub> typically occurs after the P1dB, estimated to be P1dB+10dB. A two-tone input signal

is commonly used for the IP<sub>3</sub> test. (2.7) is a system overall IIP<sub>3</sub>, it is a measure of every elements IIP<sub>3</sub>.

$$\frac{1}{IIP_3} = \frac{1}{IIP_{3,1}} + \frac{G_1}{IIP_{3,2}} + \frac{G_1G_2}{IIP_{3,3}}$$

(2.7)

Where IIP<sub>3,1</sub> is the input referred IP<sub>3</sub> of the first stage, IIP<sub>3,2</sub> is the input referred IP<sub>3</sub> of the second stage, IIP<sub>3,3</sub> is the input referred IP<sub>3</sub> of the third stage,  $G_1$  is the gain of the first stage and  $G_2$  is the gain of the second stage.

Figure 2.5 Graphical representation of the third-order intercept point and P1dB [6]

From (2.7), it is seen that the gain of the preceding stages effects directly the IIP3 of the next stages, but a low noise figure demands high gain. Here there is a tradeoff between noise and linearity [2] [7].

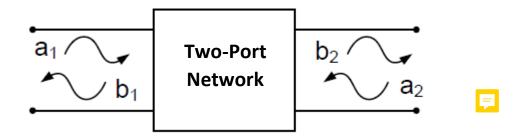

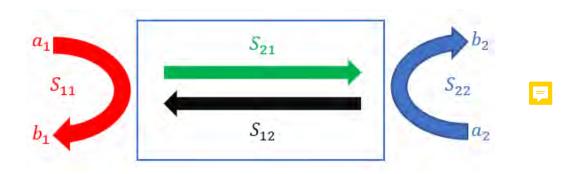

# 2.5 <u>Scattering Parameters (S-parameters)</u>

At the low frequencies, the system is characterized by measurement of open and short circuit tests, which determine the admittance and hybrid parameters. At high frequencies, the signal is dealt with as a wave, therefore low frequency methods are not possible. S-parameters are used at the high frequencies to characterize the input and output variables to measure input impedance, gain, reflections and output impedance. The S-parameters relate the input and output of electromagnetic waves as  $a_1, a_2, b_1$  and  $b_2$  when the system is viewed as a two-port network. Knowing the S-

parameters is enough to aid in designing a system without knowledge of the components it consists of.

Figure 2.6 Two-Port network incident and reflected waves.

Figure 2.7 S11, S12, S21, and S22

The S-parameters are calculated as:

$$S_{11} = \frac{b_1}{a_1} \tag{2.8}$$

$$S_{12} = \frac{b_1}{a_2} \tag{2.9}$$

$$S_{21} = \frac{b_2}{a_1} \tag{2.10}$$

$$S_{22} = \frac{b_2}{a_2} \tag{2.11}$$

Where  $S_{11}$  is the input reflection coefficient,  $S_{12}$  is the reverse gain if the input and output where swapped,  $S_{22}$  is the output reflection coefficient, and  $S_{21}$  is the gain.

### 2.6 Process, Voltage and Temperature Variations (PVT).

TVT; sometimes called corner analysis; is done to check the fabrication quality of a circuit. Process refers to the circuit elements fabrication, each different component undergoes a different process and therefore will have different dimension than that on the schematic. Even identical transistor cannot be expected to be the same size after fabrication due to errors. Voltage variation test the circuit ability to handle a supply voltage swing, an example of such variation is a battery whose supply voltage drops with use. Temperature variation are done to test the circuit under different temperatures, these temperature changes can be due to heating of the circuit component due to operation or environmental temperature changes. In this thesis the industry standard temperature is taken into consideration (-40°C →85°C).

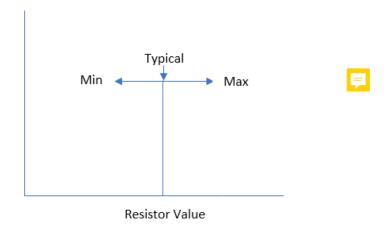

Process variation mean that elements in the circuit have a maximum, minimum, and typical values depending on the length and width when fabricated. Resistor corner analysis apply for capacitors and inductors. MOSFET corner analysis apply for BJT and diodes.

Figure 2.8 Resistor corner analysis

The resistor will take any value between Min and Max. Min, Max and Typical values are given by the foundry. If the resistor takes the min value, then its value is less than the typical, the current through the resistor increases, therefore power consumption increases (min is sometimes called "wp" meaning worst power)

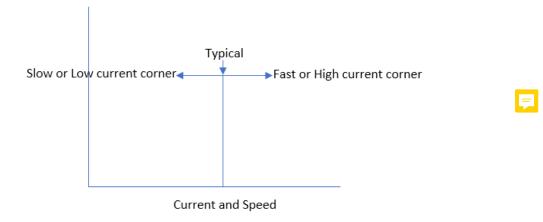

Figure 2.9 Fast, typical and slow corners

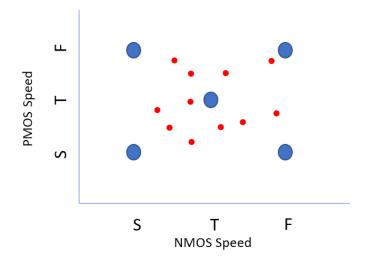

For a MOSFET process, the oxide thickness, doping concentration, length and width can vary, resulting in a change of Vth. For a MOSFET the corner analysis is: TnTp, SnSn, SnSp, SpSn, SpSp, FnFn, FnFp, FpFn and FpFp. T stand for typical, S stand for slow, F stand for fast, n and p stand for NMOS and PMOS respectively.

Figure 2.10 Corner analysis possible combinations

At the start of the design, a voltage source will be used to bias the circuit. This helps simplify the design procedure. After a biasing point has been picked, the voltage source will be replaced with transistor current mirrors and corner analysis done with the current mirrors as biasing.

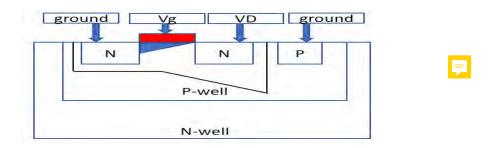

#### 2.7 Forward Body Biasing (FBB).

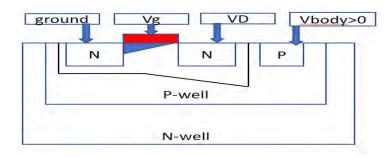

By connecting the body of the MOSFET to the gate or a DC voltage source FBB is achieved. In the case of CG, the body is directly connected to the gate, as no AC signal is present on the gate. However, for the CS, the body cannot be connected to the gate as an AC signal is present, the body is connected to its own biasing voltage or before the biasing resistor.

In [8] an 130nm ultra-low power (ULP) and ultra-low volt (ULV) was achieved using FBB and a huge circuit of 0.39mm<sup>2</sup>, it used a CG in a current-reuse structure, implied an inductor gm boosting techniques, low-power input matching was achieved by an active shunt-feedback while the current of the feedback was reused by the input of the transistor, a BW of 0.6-4.2Ghz using 0.5V and 500uA, achieving 4 NF and 14db gain. The auxiliary amplifier power was not included in the power measurement. The design of this thesis will adopt the FBB technique. In [9] an UWB 3-10Ghz CG was design with 1.1V and 2.15mW using body biasing a gain of 10.4dB, NF of 4.9 on 180nm, his paper is a letter discussing matching of CG and his chip fabrication, this letter is related to [10]. In [11] using FBB and 3 coupling inductors to achieve ULP and ULV LNA but a narrow band 400-900Mhz, voltage gain of 18.5-20.7, NF of 2.95, 0.385mW and 0.5V in 180nm.

From low power application, where power is a main concern, [8], [10], [9], [11] all have used FBB to improve the power consumption. Since the LNA will be connected to an RF harvester, any reduction in power consumption is a bonus to the design.

Figure 2.11 Cross section view of NMOS without FBB.

Figure 2.12 Cross section view of NMOS with FBB.

"DC print" option opens a window that display the transistors operating parameters at the given biasing conditions. This was used to display Vth and compare Vth with FBB vs Vth without FBB.

No FBB

FBB

Diagram

Vth

442m

391m

Table 4. FBB Vth value

From Table 4 both a transistor with FBB and without FBB are shown, the only problem with FBB occurs when the body is connected to the gate and an AC input is at the gate (such as common-source configuration) making an AC signal to the body which is undesired. One way to solve this issue is to have a separate biasing to the body, another way to connect an RF choke to the body to prevent an AC signal from passing through. An RF choke can be a resistor or an inductor. Having a separate biasing to the body is not desired as it adds another pin to the chip. The Common-gate configuration does not suffer from this issue as the gate does not have an AC input applied to it, the AC input is applied to the transistor source terminal.

<sup>\*</sup>Vth values extracted from cadence "DC Print"

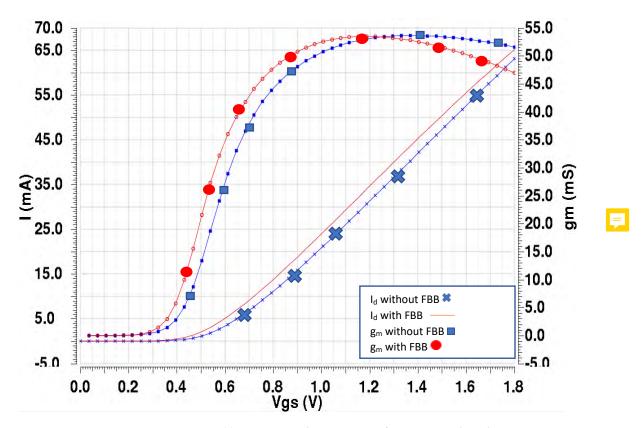

Figure 2.13 Drain current (I) vs Vgs and gm vs Vgs for FBB and without FBB

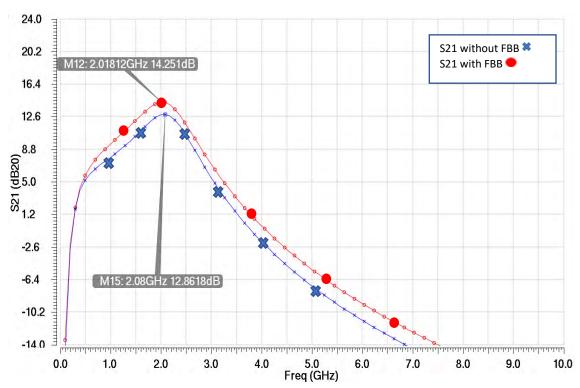

Figure 2.14 Gain with and without FBB.

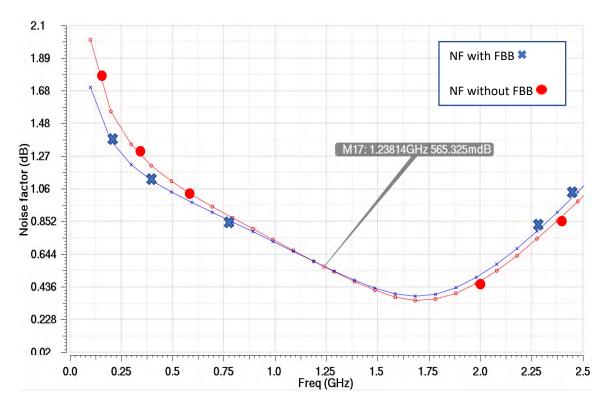

Figure 2.15 NF with and without FBB.

Figure (2.14) is the gain of the CS with FBB and without, an increase in gain of about 1.5dB due to FBB is noticed. Figure (2.15) NFmin for the CS with and without FBB. FBB reduced the noise at low frequencies and increased it in high frequencies. By connecting the gate to the bulk, Vth is decreased, hence the voltage required to turn on the device is decreased [8].

#### **Chapter 3. Low Noise Amplifiers**

3.1 oise oise factor (F) or noise figure (NF) is used to characterize the noise performance of an RF system. It represents the ratio of output noise power to the input noise power; the NF and gain are the main figure of merit for an LNA. An ideal noiseless system will add no noise, meaning F=1 or NF=0dB. In general, NF is a function of the source impedance, where the noise power is normalized and divided by source resistance,  $R_s$ . Since most RF system are designed with an input and output impedance of  $50\Omega$ , this eliminates the ambiguity of the NF definition.

The Friis equation (3.42) indicates that the noise from the block following the LNA (usually the mixer) is reduced by the gain of the LNA when referred to the input. The LNA should be placed as close to the antenna as possible so the weak RF input is first amplified with the addition of a little noise as possible before further processing. That is why the NF and gain are the two most important figure of merit of the LNA.

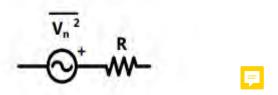

**3.1.1 Thermal noise of resistors:** The thermal noise of a resistor can be modeled as a voltage noise source in series with a noiseless resistor.

Figure 3.1 Resistor thermal noise model.

The resistor thermal noise is:

$$\overline{V_n^2} = 4KTR\Delta f \tag{3.1}$$

where K is Boltzmann's constant, T is the absolute temperature given in kelvin, and  $\Delta f$  is the bandwidth of interest in Hz.

3.1.1 Drain current noise (thermal noise) of MOSFETs: The drain current noise in the MOSFET is can be modeled as current source connected in parallel between the drain and source with the  $g_m$  of the transistor. Its power is given as [12]:

$$\overline{\iota_n^2} = 4KT\gamma g_{do}\Delta f \tag{3.2}$$

where  $\gamma =$  McWhorther tunneling parameter (2/3 for long channel) and  $g_{do} =$   $g_m/\alpha$

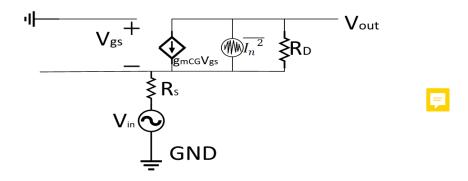

Common gate noise due to drain noise when the output is connected to ground:

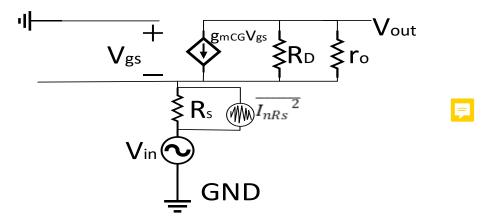

Figure 3.2 Common gate small signal model with thermal noise

$$I_s = g_m v_{qs} + \overline{I_n} \tag{3.3}$$

$$I_{s} = -g_{m}I_{s}R_{s} + \overline{I_{n}} \tag{3.4}$$

$$I_s = \frac{\overline{I_n}}{1 + g_m R_s} \tag{3.5}$$

$$\overline{I_{out}} = I_s \tag{3.6}$$

$$\overline{I_{out}}^2 = I_s^2 \tag{3.7}$$

$$\overline{I_{out}^2} = \left(\frac{\overline{I_n}}{1 + g_m R_s}\right)^2 \tag{3.8}$$

$$\overline{I_{out}^2} = 4KT\gamma g_{do} \left(\frac{1}{1 + g_m R_s}\right)^2 \tag{3.9}$$

Noise due to source resistance when the output is connected to ground:

Figure 3.3 Common gate small signal model with source resistor thermal noise

$$\overline{I_{s-out}} = g_m V_{qs} \tag{3.10}$$

Using voltage division:

$$V_{gs} = \frac{\frac{1}{g_m}}{\frac{1}{g_m} + R_s} \overline{V_n} \tag{3.11}$$

Therefore:

$$\overline{I_{s-out}} = (g_m) \frac{\frac{1}{g_m}}{\frac{1}{g_m} + R_s} \overline{V_n}$$

(3.12)

Squaring:

$$\overline{I_{s-out}^{2}} = (g_{m}^{2}) \frac{\frac{1}{g_{m}^{2}}}{\left(\frac{1}{g_{m}} + R_{s}\right)^{2}} 4KTR_{s}$$

(3.13)

$$=\frac{g_m^2}{(1+g_m R_s)^2} 4KTR_s \tag{3.14}$$

Dividing the drain noise by the source noise:

$$\frac{\overline{I_{out}^{2}}}{I_{s-out}^{2}} = \frac{4KT\gamma g_{do} \left(\frac{1}{1+g_{m}R_{s}}\right)^{2}}{\frac{g_{m}^{2}}{(1+g_{m}R_{s})^{2}} 4KTR_{s}} = \frac{\gamma g_{do}}{g_{m}^{2}R_{s}}$$

(3.15)

Finally, the known equation of F is derived:

$$F = \frac{\overline{I_{s-out}^2}}{\overline{I_{s-out}^2}} + \frac{\overline{I_{out}^2}}{\overline{I_{s-out}^2}} = 1 + \frac{\gamma g_{do}}{g_m^2 R_s}$$

(3.16)

$$=1+\frac{\gamma}{\alpha g_m R_s}\tag{3.17}$$

\*If  $1/g_m = R_s$ ,

$$F = 1 + \frac{\gamma}{\alpha} \tag{3.18}$$

where  $\gamma$  is excess noise factor (2/3 in long channel devices) and  $\alpha$  is  $g_m/g_{do}$  ( $g_{do}$  is the channel resistance when  $V_{ds}=0$ ).

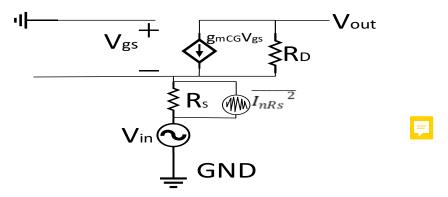

Common gate noise due to drain noise, when the output is connected to ground and channel length modulation  $(r_o)$  is considered  $(r_o = 1/g_d)$ :

Figure 3.4 Common gate small signal model with thermal noise and channel length modulation

$$I_s = g_m v_{qs} + \overline{I_n} - v_s g_d \tag{3.19}$$

$$I_s = -g_m I_s R_s + \overline{I_n} - I_s R_s g_d \tag{3.20}$$

$$I_{s} = \frac{\overline{I_{n}}}{1 + q_{m}R_{s} + R_{s}q_{d}} \tag{3.21}$$

$$\overline{I_{out}} = I_s \tag{3.22}$$

$$\overline{I_{out}}^2 = I_s^2 \tag{3.23}$$

$$\overline{I_{out}^2} = \left(\frac{\overline{I_n}}{1 + g_m R_s + R_s g_d}\right)^2 \tag{3.24}$$

$$\overline{I_{out}^{2}} = 4KT\gamma g_{do} \left(\frac{1}{1 + g_{m}R_{s} + R_{s}g_{d}}\right)^{2}$$

(3.25)

Equation (3.25) is the CG thermal noise equation when the channel length modulation is taken into consideration. Since  $g_d$  is in the denominator, increasing it will result in less noise, this means the lower the channel length modulation parameter  $(r_0)$  is, the larger  $g_d$  is and less noise is produced. Lowering  $r_0$  is also desirable for its negative effect on the gain of the transistor.

Noise due to source resistance, when the output is connected to ground and channel length modulation  $(r_o)$  is considered  $(r_o = 1/g_d)$ :

Figure 3.5 Common gate small signal model with source resistance thermal noise and channel length modulation

$$\overline{I_{s-out}} = g_m V_{gs} + V_{gs} g_d = V_{gs} (g_m + g_d)$$

(3.26)

Using voltage division:

$$V_{gs} = \frac{\frac{1}{g_m} \| r_o}{\frac{1}{g_m} \| r_o + R_s} \overline{V_n}$$

(3.27)

$$=\frac{r_o}{r_o+g_m r_o R_s+R_s} \overline{V_n} \tag{3.28}$$

$$=\frac{1}{1+g_m R_s + R_s g_d} \overline{V_n} \tag{3.29}$$

Therefore:

$$\overline{I_{s-out}} = \frac{(g_m + g_d)}{1 + g_m R_s + R_s g_d} \overline{V_n}$$

(3.30)

Squaring:

$$\overline{I_{s-out}^{2}} = \left(\frac{(g_m + g_d)}{1 + g_m R_s + R_s g_d}\right)^2 4KTR_s \tag{3.31}$$

Dividing the drain noise by the source noise:

$$\frac{\overline{I_{out}^{2}}}{I_{s-out}^{2}} = \frac{4KT\gamma g_{do} \left(\frac{1}{1+g_{m}R_{s}+R_{s}g_{d}}\right)^{2}}{\left(\frac{(g_{m}+g_{d})}{1+g_{m}R_{s}+R_{s}g_{d}}\right)^{2} 4KTR_{s}}$$

(3.32)

$$=\frac{\gamma g_{do}}{(g_m + g_d)^2 R_s} \tag{3.33}$$

Finally, F is derived:

$$F = \frac{I_{s-out}^{2}}{I_{s-out}^{2}} + \frac{\overline{I_{out}^{2}}}{I_{s-out}^{2}}$$

(3.34)

$$=1+\frac{\gamma g_{do}}{(g_m+g_d)^2 R_s}=1+\frac{\gamma g_m}{\alpha (g_m+g_d)^2 R_s}$$

(3.35)

\*if  $r_o$  is large, then  $g_d$  is small and  $1/g_m = R_s$ . Equation (3.42) becomes:

$$g_m + g_d \approx g_m \tag{3.36}$$

$$F = 1 + \frac{\gamma g_m}{\alpha (g_m)^2 R_s} \tag{3.37}$$

$$F = 1 + \frac{\gamma}{\alpha} \tag{3.38}$$

Equation (3.18) is the same noise equation as (3.38) if channel length modulation resistance is assumed to be large. Meaning whether channel length modulation is considered or not, the same noise can be derived.

**3.1.2 Noise figure:** Noise Figure indicates the noise deterioration of a block. It is defined as the ratio of input signal-to-noise ratio (SNR<sub>in</sub>) to output signal-to-noise ratio (SNR<sub>out</sub>).

$$NF(dB) = 10\log(NR) = 10\log\left(\frac{SNR_{in}}{SNR_{out}}\right)$$

(3.39)

where NF is the Noise Figure and NR is the Noise Ratio.

One can approximate the NR of the receiver using Friis Formula as:

$$NR_{RX} = NF_{LNA} + \frac{NF_{rest} - 1}{Gain_{LNA}} \tag{3.40}$$

NF<sub>rest</sub> is the noise factor of the following stages.

**3.1.3 Flicker noise:** Flicker noise is associated with MOSFETs only, also known as pink noise. The flicker noise equation is:

$$\overline{\iota_n^2} = Kg_m^2 \frac{1}{f} \frac{1}{WLC_{ox}^2}$$

(3.41)

where K is a process dependent constant, W is the channel width and L is the channel length

Flicker noise heavily appears in low frequencies, around the DC point, thus acting as a DC offset. This will damage the signal after mixing, since the signal after mixing is down converted to low frequencies. Therefore, some DC blockage is needed. Reducing flicker noise can be done by increasing gate voltage.

#### 3.2 Low Noise Amplifiers

The LNA, Low Noise Amplifier, is an essential building block for receivers of wireless circuit. The signals received at the antenna are weak and must be amplified so that they can be processed. This amplification must be done with care to add as little additional noise as possible, this way the signal proceeds to the rest of the circuit in the best possible conditions. According to the Friis' formula, which shows the relation between the signal-to-noise ratio (SNR), the noise factor (F) of a system can be represented in cascade as:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_m - 1}{G_1 G_{2 \dots G_{m-1}}}$$

(3.42)

where  $F_m$  and  $G_m$  are the noise factor and power gain of the m<sup>th</sup> stage. Looking at (3.1), the dominant factor of the noise is the first stage, which is usually the LNA.

To maximize the gain, the power transmission should be maximized. This is done by making sure no reflection of the signal occurs at the input or output of any elements, not just the LNA. The reflected signals are considered as noise. The absence of reflection can be insured with proper matching networks.

In addition to gain and noise requirements, the LNA must be as linear as possible, as mentioned in Chapter 2, nonlinearity results in IMD terms that degrade the selectivity

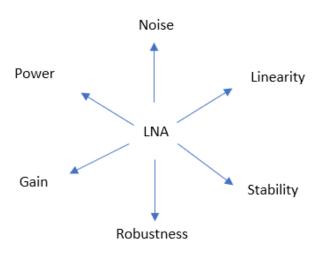

of the receiver. There is a tradeoff between noise and linearity in the design of an LNA. Figure (3.6) shows the LNA's design tradeoffs, where one parameter is reduced to increase another. Although the main priority is low noise, having little gain or an unstable LNA is not acceptable.

Figure 3.6 LNA trade-offs.

# 3.3 NA Topologies

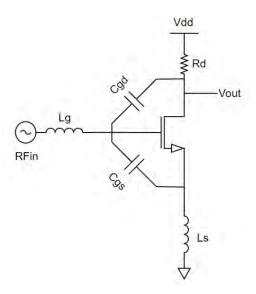

3.3.1 Common-source low-noise amplifier: The resistive input impedance can be achieved by adding an inductor in series with the gate  $(L_g)$  and an inductor in series with the source  $(L_s)$ . Connecting a resistor or an inductor at the source of a CS is also known as degeneration. The CS LNA suffers from parasitic capacitors gate-drain capacitor  $C_{gs}$  and gate-source capacitor  $C_{gd}$ .  $C_{gd}$  provides a feedforward path from the input to output which decreases the reverse isolation, it can also interact with an inductive load making a negative resistance at the input, causing stability issues. To simplify calculations  $C_{gd}$  will be ignored, the impact of ignoring the capacitor  $C_{gd}$  in calculation is the increase of calculated bandwidth, gain and missing a pole of the circuit. The problem with missing a pole is if the pole itself is positive, the circuit becomes conditionally stable, poles do not need to be calculated as another stability test is chosen for the LNA. Figure (3.7) is the CS topology with the parasitic capacitors.

Figure 3.7 Common-Source with parasitic capacitors shown.

The input impedance of a CS with  $L_g$  and  $L_s$ :

$$Z_{in} = s(L_g + L_s) + \frac{1}{sC_{gs}} + \frac{g_m}{C_{gs}} L_s$$

(3.43)

In  $Z_{in}$  there is resistive components in the input impedance. To get purely resistive  $Z_{in}$ ,  $L_g$  and  $L_s$  should take values to resonate out the  $C_{gs}$  at the operating frequency with  $(g_m/C_{gs})L_s$  set to  $R_s$  ( $R_s$  is usually set to 50).

$$j\omega_o(L_g + L_s) + \frac{1}{j\omega_o C_{qs}} = 0 (3.44)$$

$$\frac{g_m}{C_{qs}}L_s = R_s \tag{3.45}$$

$$\frac{g_m}{C_{as}} \approx \omega_T \tag{3.46}$$

The main advantage of this topology is that the inductor synthesizes with the resistive component of the input impedance making it noiseless, unlike other topologies where a resistor is added in the signal path to provide the input impedance matching [13], this explains the low-noise performance and popularity of the inductive degenerated CS LNA. the main disadvantage is the extra cost of the circuit and the increase of size of the chip due to inductors generally being large.

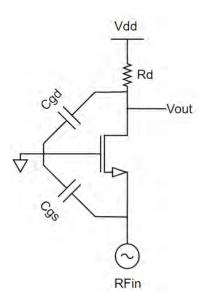

**3.3.2 Common-gate low-noise amplifier:** In CG LNA the gate is AC shorted to ground and input signal is at the source terminal. The resistance looking into the source is  $1/g_m$  when channel length modulation and body effect are ignored, this provides a simple input matching condition to  $R_s$  where  $1/g_m = R_s$  satisfies the input matching. Unlike the CSLNA, there is no miller effect associated with the CG parasitic capacitance, this results in better isolation and a higher bandwidth. However, the CG suffers from a noisy channel conductance in the signal path, resulting in a higher NF. The F of the CG can be approximated to be, as derived in this chapter:

$$F = 1 + \frac{\gamma}{\alpha} \tag{3.47}$$

Although the CG offers a high bandwidth and an easier matching conditions, low power consumption and compact size (inductorless) [7], it suffers from higher noise and lower voltage gain than the CS [14].

Figure 3.8 Common-Gate with parasitic capacitors shown.

Figures (3.7) and (3.8) show the two main parasitic capacitors of a transistor,  $C_{gs}$  and  $C_{gd}$ . They are responsible for the bandwidth limitation of transistors, unfortunately they are unavoidable and are due to the physical structure of the transistors.

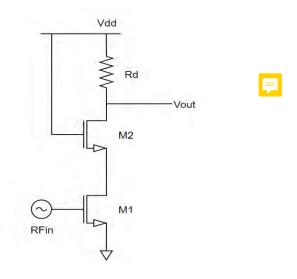

**3.3.3 Cascode structure:** A cascode LNA structure is used with a CS. Instead of the drain of the CS connected to  $R_D$ , it is connected to the source of a second transistor which acts like a CG. The cascode structure reduces the miller effect of the CS stage which improves the bandwidth and improves input/output isolation. Having better input/output isolation improves stability and makes the input and output matching independent of each other.

Figure 3.9 Cascode structure.

Unfortunately, the cascode structure does require more headroom voltage and increases the total noise of the LNA due to M2 noise contribution.

**3.3.4 Differential LNA:** Any single ended design can be transformed into a differential pair by adding a mirror copy of the original single stage and connecting the sources. The main advantage of a differential design is its ability to cancel any common mode noise, such as thermal and supply noise. A balanced LNA is a differential LNA but a differential LNA is not necessarily a balanced one. Balanced LNA referred to the differential LNA with both output nodes equal in voltage.

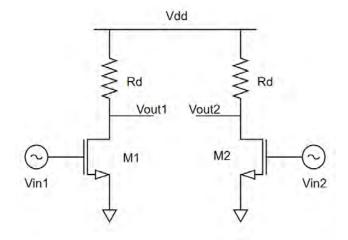

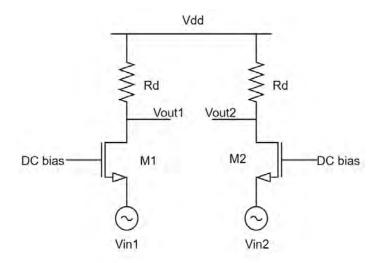

Figures (3.10) and (3.11) are CS and CG differential amplifiers respectively, each with its own set of uses. the CS amplifiers takes the AC input from the gate while the CG amplifier takes the AC input to the source.

Figure 3.10 CS differential pair.

Figure 3.11 CG differential pair.

Differential signaling is preferred to reduce second-order distortion and to reject power supply, substrate, and thermal noise. Single input is preferred to save pins, but not necessarily area, as one bulky transistor might consume more power and chip area than two transistor working in differential pair [7].

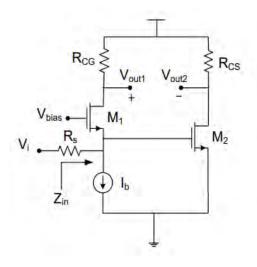

Combining a CG and a CS differential amplifier will result in what is known as a Balun amplifier. The Balun amplifier is studied in this thesis, deriving a new noise figure, an improved noise figure and simulating it when powered by a harvester. It is known to be an unbalanced output design with a set condition to fix the unbalance issue while still maintaining a wideband.

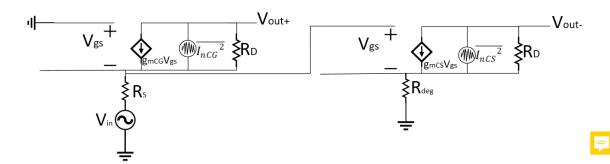

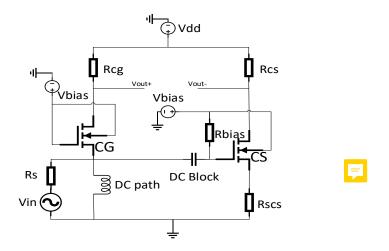

3.3.5 Balun LNA: A differential amplifier that combines a common-gate and common-source acting as a differential pair is known as the Balun LNA, the input of the LNA is applied to both CS and CG at the same time. The Wideband Balun LNA with resistors represented in figure (3.12) has two stages: a common gate (CG) and a common-source (CS) stage. This circuit has the functionality of Balun because the entry of the LNA has a single-ended input and delivers a differential output, the resisters are used as current drivers, and can be replaced by MOSFETS, making it a MOSFET only Balun LNA, which makes the circuit smaller, reduces cost, process and supply variation [6].

Figure 3.12 Balun LNA.

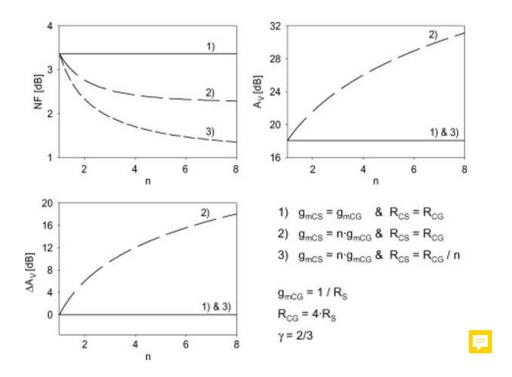

In [15], a thorough study on Balun LNA has been made and concluded with 3 main equation regarding the sizing of the transistor and how to make sure Balun effect is achieved. Also, it studied the gain imbalances that can appear if not sized properly. It also discusses how to achieve the maximum gain and least noise figure. Figure (3.13) are the graphs showing NF, gain and gain imbalance vs 'n' factor. The n factor represents a multiplier for the  $g_m$  and resistors. For the best noise performance, the third set of condition must be applied. And for purely more gain, second set is preferred.

In this chapter, a new noise figure is derived for the Balun LNA showing that the thermal noise can be completely canceled and an additional improvement on how to cancel the thermal noise and balance the output using a degeneration resistor at the common-source side.

Figure 3.13 Balun LNA equations and graphs.

The output can be balanced if the magnitudes of the gains of the two stages are adjusted to an approximate value, because the common-source (CS) stage has the function of an inverter, while the common-gate (CG) does not, the differential voltage gain is taken between the drains of the two transistors. Their expression is as follow [16]:

$$A_{voutCG} = (g_{mCG} + g_{mbCG})(R_{CG} \parallel ro_{CG})$$

(3.48)

where  $g_{mCG}$  is the transconductance of the CG,  $g_{mbCG}$  is the body effect of the CG,  $R_{CG}$  is the drain resistance of the CG and  $ro_{CG}$  is channel length modulation of the CG,

$$A_{voutCS} = (-g_{mCS})(R_{CS} \parallel ro_{CS})$$

(3.49)

where  $g_{mCS}$  is the transconductance of the CS,  $R_{CS}$  is the drain resistance of the CS and  $ro_{CS}$  is channel length modulation of the CS

The differential gain is given by:

$$A_{vdiff} = A_{voutCG} - A_{voutCS} (3.50)$$

The input impedance is [6]:

$$R_{in} = \frac{1 + (\frac{1}{ro_{CG}}R_{CG})}{g_{mcG} + g_{mbcG} + \frac{1}{r_{ocG}}}$$

(3.51)

To cancel the noise contribution of the first stage, the common-gate (CG) stage, is possible if both stages have the same voltage gain. This happens because the first stage's noise appears as a common-mode signal at the differential output [6] [15]. According to [15], if the (CS) linearity is assured, the circuit will have good linearity. Also, according to [15], the noise factor is (the CS noise referred to the input was ignored).

$$F = 1 + \frac{\gamma g_{mcG} (R_{CG} - R_S g_{mcS} R_{CS})^2}{R_S A^2_V} + \frac{\gamma g_{mcS} R_{CS}^2 (1 + g_{mcG} R_S)^2}{R_S A^2_V} + \frac{(R_{CG} + R_{CS} (1 + g_{mcG} R_S))^2}{R_S A^2_V}$$

(3.52)

Figure 3.14 Improved Balun.

Figure (3.14), the design is a single input and single output improved Balun [17]. The output buffer is to avoid any loading effect and to have an output impedance as high as possible. The buffer power consumption was not included in the power measurement. The same idea will be applied to the design, where buffers will be added for isolation and their power consumption not taken into consideration. Also, no new noise figure was derived, which this thesis will do.

In [8] an 130nm ultra-low power (ULP) and ultra-low volt (ULV) was achieved using FBB and a huge circuit of 0.39mm<sup>2</sup>, it used a CG in a current-reuse structure, implied an inductor gm boosting techniques, low-power input matching was achieved by an active shunt-feedback while the current of the feedback was reused by the input

of the transistor, a BW of 0.6-4.2Ghz using 0.5V and 500uA, achieving 4 NF and 14db gain. The auxiliary amplifier power was not included in the power measurement. The design of this thesis will adopt the FBB technique.

In [18], a Balun LNA was used with a CG stage before the Balun itself for matching purposes, but no CS degeneration resistor was added. In [19], Balun LNA was used, with cascaded structure on the CG, but no new noise figure was derived and no CS degeneration was used. In [20], instead of a global negative feedback technique which helps in improving NF and matching at the price of stability, a feedforward noisecanceling technique was used allowing for noise and impedance matching, while canceling the distortion and noise of the matching amplifiers. In [21], a resistive feedback was used to increase the bandwidth, the NF was improved by adding a gmenhanced cascaded amplifiers with a source follower feedback. In [22], a Balun LNA and a wide tuning range synthesizer is used to cover major frequency bands of use today, the design does include a mixer and a programmable integration sampler and clock discrete-time filters, although the emphasis of the measurement where the LNA, no new noise figure or degeneration source where used. In [23], an ESD-protected Balun LNA with an inductorless broadband input matching is offered, the amplification stage exploited double current reuse and a single-stage thermal noise cancellation to enhance the gain, NF and power consumption. In [24], an inductorless Balun LNA for low power multiband and multi-standard radios is proposed, the LNA uses dual shunt feedback to reduce the bias current needed by the CG while this current is reused in the CS stage, the NF is derived but for the whole system not just the Balun LNA. In [25], a new modified current-bleeding (CBLD) technique was used to cancel the noise of the Balun LNA, this method helps solve the issue of balancing the Balun with different resistors causing phase mismatch due to different RC constant. A comparison between the conventional and modified CBLD technique is tested, the modified CBLD uses an extra resistor at the drain of the MOSFET in the CBLD circuit, this increases the input impedance seen by the source of the CBLD circuit (due to channel length modulation), therefore reducing the overall noise, unfortunately, the Balun NF derived is a cascaded structure Balun and not useful for this papers analysis.

In this thesis, a complete noise analysis will be derived. Showing how the thermal noise of both the CG and the CS of the Balun LNA can be canceled. Also, a degeneration resistor will be added to the CS stage of the Balun

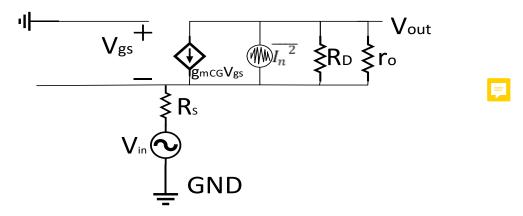

## 3.4 Balun LNA Noise Analysis

The thermal noise of the Balun LNA will be analyzed fully, with CS thermal noise taken into consideration and showing how balancing the LNA will completely remove the thermal noise of both the CS and CG. Then, an additional analysis of the Balun LNA with degeneration resistor is derived, where it is shown how the degeneration resistor can cancel the thermal noise of both the CS and CG stage.

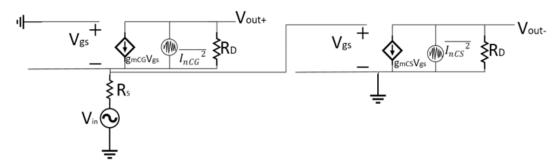

**3.4.1 Noise analysis without degeneration resistor:** First, the thermal noise analysis of the Balun LNA with the thermal noise of the CS stage taken into consideration [26]:

Figure 3.15 Balun LNA small signal model with thermal noise.

The gain of the CG is given by:

$$A_{\nu CG} = g_{mCG} R_{CG} \tag{3.53}$$

The gain of the CS is given by:

$$A_{vCS} = -g_{mCS}R_{CS} \tag{3.54}$$

The gain of the LNA is the difference between CG and CS gains:

$$A_{vLNA} = g_{mCG}R_{CG} + g_{mCS}R_{CS} (3.55)$$

The voltage noise of the CG:

$$\overline{Vout_{CG}} = \overline{I_{nCG}}R_{CG} \tag{3.56}$$

CG noise referred to the input:

$$\overline{Vin_{CG}} = \frac{\overline{I_{nCG}}R_{CG}}{|A_{vCG}|} = \frac{\overline{I_{nCG}}}{g_{mCG}}$$

(3.57)

The output voltage noise of the CS:

$$\overline{Vout_{CS}} = \overline{I_{nCS}}R_{CS} \tag{3.58}$$

The CS noise referred to the input:

$$\overline{Vin_{CS}} = \frac{\overline{I_{nCS}}R_{CS}}{|A_{vCS}|} = \frac{\overline{I_{nCS}}}{g_{mCS}}$$

(3.59)

Total output noise of the CG when considering the input referred noise of the CS is:

$$\overline{Vout_{CG,total}} = \overline{I_{nCG}}R_{CG} + \frac{\overline{I_{nCS}}}{g_{mCS}} * g_{mCG}R_{CG}$$

(3.60)

The total output voltage noise of the CS when considering the input referred voltage noise of the CG is also given by:

$$\overline{Vout_{CS,total}} = \overline{I_{nCS}}R_{CS} + \frac{\overline{I_{nCG}}}{g_{mCG}} * g_{mCS}R_{CS}$$

(3.61)

The voltage noise of the source is:

$$\overline{V_{ns}} = \overline{V_n} * \left(\frac{R_{in}}{R_{in} + R_s}\right) \tag{3.62}$$

And  $\overline{V_n^2}$  is the power of the noise given to be [6]:

$$\overline{V_n^2} = 4KTR_S \tag{3.63}$$

Assuming,  $R_{in} = \frac{1}{g_{mcG}}$ , which is the low frequency matching condition of the CG

Therefore,

$$\overline{V_{ns}} = \overline{V_n} * \left(\frac{1}{1 + g_{mCG}R_S}\right) \tag{3.64}$$

where K is Boltzmann constant, T is temperature in kelvin and R is the source resistance

Total voltage noise of the LNA:

$$\overline{Vout_{LNA}} = \overline{Vout_{CG,total}} - \overline{Vout_{CS,total}}$$

(3.65)

Dividing by noise of the source resistance:

$$\frac{\overline{Vout_{LNA}}}{\overline{V_{nS}}} = \left(\overline{Vout_{CG,total}} - \overline{Vout_{CS,total}}\right) * \frac{1 + g_{mCG}R_S}{\overline{V_n}}$$

(3.66)

Substituting the proper terms and simplifying:

$(\overline{V_n}$  was moved to the left side to ease calculation):

$$\frac{Vout_{LNA}}{\overline{V_{ns}}} * \overline{V_{n}} =$$

$$\left(\overline{I_{nCG}}R_{CG} + \frac{\overline{I_{nCS}}}{g_{mCS}} * g_{mCG}R_{CG} + \overline{I_{nCG}}R_{CG}g_{mCG}R_{S}\right) + \frac{\overline{I_{nCS}}}{g_{mCS}} * g_{mCG}R_{CG}g_{mCG}R_{S}$$

$\left[ \overline{I_{nCS}} R_{CS} + \frac{\overline{I_{nCG}}}{g_{mCG}} * g_{mCS} R_{CS} + \overline{I_{nCS}} R_{CS} g_{mCG} R_{S} \right] + \frac{\overline{I_{nCG}}}{g_{mCG}} * g_{mCS} R_{CS} g_{mCG} R_{S}$ (3.67)

Grouping terms containing  $\overline{I_{nCG}}$ :

$$\overline{I_{nCG}}R_{CG} + \overline{I_{nCG}}R_{CG}g_{mCG}R_{S} - \frac{\overline{I_{nCG}}}{g_{mCG}} * g_{mCS}R_{CS} - \frac{\overline{I_{nCG}}}{g_{mCG}}g_{mCS}R_{CS}g_{mCG}R_{S}$$

(3.68)

Grouping terms containing  $\overline{I_{nCG}}$  into two terms:

$$\overline{I_{nCG}} \left( R_{CG} - \frac{1}{g_{mCG}} * g_{mCS} R_{CS} g_{mCG} R_s \right)$$

$$= \overline{I_{nCG}} (R_{CG} - R_{CS} g_{mCS} R_s)$$

(3.69)

$$\overline{I_{nCG}}\left(R_{CG}g_{mCG}R_{S} - \frac{\overline{1}}{g_{mCG}} * g_{mCS}R_{CS}\right)$$

(3.70)

Grouping terms containing  $\overline{I_{nCS}}$ :

$$\frac{\overline{I_{nCS}}}{g_{mCS}} * g_{mCG}R_{CG} + \frac{\overline{I_{nCS}}}{g_{mCS}} * g_{mCG}R_{CG}g_{mCG}R_{S} - \overline{I_{nCS}}R_{CS} - \overline{I_{nCS}}R_{CS}g_{mCG}R_{S}$$

$$= \overline{I_{nCS}} \left( \frac{1}{g_{mCS}} * g_{mCG}R_{CG} + \frac{1}{g_{mCS}} * g_{mCG}R_{CG}g_{mCG}R_{S} - R_{CS} - R_{CS}g_{mCG}R_{S} \right) (3.71)$$

After grouping the noise terms with their respective noise currents, next step is to add them back and square to get the noise power:

$$\frac{\overline{Vout_{LNA}}^{2}}{\overline{V_{ns}}^{2}} * \overline{V_{n}}^{2} = \frac{\overline{I_{ncG}}^{2}}{I_{ncG}^{2}} (R_{CG} - R_{CS}g_{mcS}R_{s})^{2} + \frac{\overline{I_{ncG}}^{2}}{g_{mcG}^{2}} \left( R_{CG}g_{mcG}R_{s} - \frac{\overline{1}}{g_{mcG}} * g_{mcs}R_{cs} \right)^{2} + \frac{\overline{I_{ncG}}^{2}}{I_{ncG}^{2}} \left| (R_{CG} - R_{CS}g_{mcS}R_{s}) \left( R_{CG}g_{mcG}R_{s} - \frac{\overline{1}}{g_{mcG}} * g_{mcs}R_{cs} \right) \right| + \frac{\overline{I_{ncG}}^{2}}{I_{ncS}^{2}} \left( \frac{1}{g_{mcS}} * g_{mcG}R_{cG} + \frac{1}{g_{mcS}} * g_{mcG}R_{cG}g_{mcG}R_{s} \right)^{2} - R_{CS} - R_{CS}g_{mcG}R_{s} \right)^{2}$$

(3.72)

Finally, dividing by the gain of the LNA squared to refer the noise to the input:

$$\begin{split} \overline{Vin_{LNA}}^2 &= \\ \frac{\gamma g_{mCG} (R_{CG} - R_{CS} g_{mCS} R_s)^2}{R_s * A_{vLNA}^2} + \\ \frac{\gamma g_{mCG} \left( R_{CG} g_{mCG} R_s - \frac{\overline{1}}{g_{mCG}} * g_{mCS} R_{CS} \right)^2}{R_s * A_{vLNA}^2} + \end{split}$$

$$\frac{\gamma g_{mCG}\left|\left(R_{CG}-R_{CS}g_{mCS}R_{s}\right)\left(R_{CG}g_{mCG}R_{s}-\frac{\overline{1}}{g_{mCG}}*g_{mCS}R_{CS}\right)\right|}{R_{s}*A_{vLNA}{}^{2}}+$$

$$\frac{\gamma g_{mCS} \left(\frac{1}{g_{mCS}} * g_{mCG} R_{CG} + \frac{1}{g_{mCS}} * g_{mCG} R_{CG} g_{mCG} R_{S}\right)^{2}}{-R_{CS} - R_{CS} g_{mCG} R_{S}}}{R_{S} * A_{vLNA}^{2}}$$

(3.73)

The total NF is:

$$F = 1 + \overline{Vin_{LNA}^2} + \frac{(R_{CG} + R_{CS})(1 + g_{mCG}R_S)^2}{R_S A_V^2}$$

(3.74)

$$g_{mCS} = ng_{mCG} (3.75)$$

$$R_{CS} = \frac{R_{CG}}{n} \tag{3.76}$$

$$R_S = \frac{1}{g_{mcG}} \tag{3.77}$$

Substituting the balancing condition (3.75)-(3.77) from [15], into equation (3.73) will result in zero thermal noise.

**3.4.2** Noise analysis with degeneration resistor: Another set of equations revolving around a CS degeneration resistor to balance the output and cancel the thermal noise is derived in [27]. If one would ignore condition set in [15], and balance the Balun LNA with a degeneration resistor at the common source; assuming CS gain is higher than CG gain.

Balancing the LNA with  $R_{SCS}$ :

Figure 3.16 Balun LNA small signal model with thermal noise and CS degeneration resistor

The gain of the CG is given by:

$$A_{vCG} = g_{mCG}R_{CG} \tag{3.78}$$

The gain of the CS is given by:

$$A_{vCS} = -\frac{g_{mCS}R_{CS}}{1 + g_{mCS}R_{SCS}} \tag{3.79}$$

The voltage noise of the CG:

$$\overline{Vout_{CG}} = \overline{I_{nCG}}R_{CG} \tag{3.80}$$

CG noise referred to the input:

$$\overline{Vin_{CG}} = \frac{\overline{I_{nCG}}R_{CG}}{|A_{\nu CG}|} = \frac{\overline{I_{nCG}}}{g_{mCG}}$$

(3.81)

The output voltage noise of the CS:

$$\overline{Vout_{CS}} = \overline{I_{nCS}}R_{CS} \tag{3.82}$$

The CS noise referred to the input:

$$\overline{Vin_{CS}} = \frac{\overline{I_{nCS}}R_{CS}}{|A_{vCS}|} = \frac{\overline{I_{nCS}}(1 + g_{mCS}R_{SCS})}{g_{mCS}}$$

(3.83)

Total output noise of the CG when considering the input referred noise of the CS is (using the above equations):

$$\overline{Vout_{CG,total}} = \overline{I_{nCG}}R_{CG} + \frac{\overline{I_{nCS}}(1 + g_{mCS}R_{SCS})}{g_{mCS}} * g_{mCG}R_{CG}$$

(3.84)

The total output voltage noise of the CS when considering the input referred voltage noise of the CG is also given by:

$$\overline{Vout_{CS,total}} = \overline{I_{nCS}}R_{CS} + \frac{\overline{I_{nCG}}}{g_{mCG}} * \frac{g_{mCS}R_{CS}}{1 + g_{mCS}R_{SCS}}$$

(3.85)

The voltage noise of the source is:

$$\overline{V_{ns}} = \overline{V_n} * \left(\frac{R_{in}}{R_{in} + R_s}\right) \tag{3.86}$$

And  $\overline{V_n^2}$  is the power of the noise given to be [6]:

$$\overline{V_n^2} = 4KTR_S \tag{3.87}$$

Assuming,  $R_{in} = \frac{1}{g_{mcg}}$ , which is the low frequency matching condition of the CG

Therefore,

$$\overline{V_{ns}} = \overline{V_n} * \left(\frac{1}{1 + g_{mCG}R_s}\right) \tag{3.88}$$

Where K is Boltzmann constant, T is temperature in kelvin and R is the source resistance

Total voltage noise of the LNA:

$$\overline{Vout_{LNA}} = \overline{Vout_{CG,total}} - \overline{Vout_{CS,total}}$$

(3.89)

Diving by noise of the source resistance:

$$\frac{\overline{Vout_{LNA}}}{\overline{V_{nS}}} = \left(\overline{Vout_{CG,total}} - \overline{Vout_{CS,total}}\right) * \frac{1 + g_{mCG}R_S}{\overline{V_n}}$$

(3.90)

Substituting the proper terms and simplifying:

$(\overline{V_n} \ was \ moved \ to \ the \ left \ side \ to \ ease \ calculation)$ :

$$\frac{\overline{Vout_{LNA}}}{\overline{V_{ns}}} * \overline{V_n} =$$